**TMP1827**

ZHCSR23 - SEPTEMBER 2022

# 具有 SHA-256-HMAC 认证引擎, 2kbit EEPROM 的 TMP1827 单线 ±0.3°C 精度温 度传感器

# 1 特性

- 具有多点共享总线和 CRC 的单线接口

- 总线供电的工作电压为 1.7V 至 5.5V

- IEC 61000-4-2 ESD 用于 8kV 接触放电

- 高精度数字温度传感器:

- - 20°C 至 +85°C 范围内为 ±0.1°C ( 典型值 ) / ±0.3°C(最大值)

- 55°C 至 +125°C 范围内为 ±0.3°C(典型值)/ ±0.5°C(最大值)

- - 55°C 至 +150°C 范围内为 ±0.5°C ( 典型值 ) / ±1.0°C(最大值)

- 有效电流为 100μA(典型值)和关断电流为 1.0μA (典型值)

- 16 位温度分辨率: 7.8125m°C (1LSB)

- 超速速度下的快速数据速率为 90kbps

- 灵活的用户可编程短地址模式,用于更快的器件寻

- SHA-256-HMAC 认证方案

- 以符合 FIPS 180-4 的安全散列标准实施

- 以符合 FIPS 198-1 标准的 HMAC 算法实施

- 2Kbit EEPROM 功能:

- 64 位块大小的写操作

- 连续读取模式

- 带写保护的读取,页面大小为 256 位

- 页面大小为 256 位的认证写保护模式

- 读/写电流为 95µA/178µA ( 典型值 )

- 用于器件寻址的 NIST 可追溯出厂编程不可擦除 64 位标识号

- 4个可配置的开漏数字输入输出和温度警报

#### 2 应用

- 工厂自动化和控制

- 电器

- 医疗配件

- CPAP 呼吸机

- 电池组

- 冷链应用

- 温度变送器

- 电动汽车充电基础设施

# 3 说明

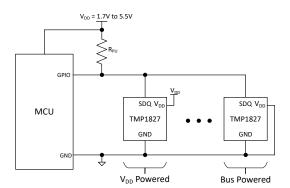

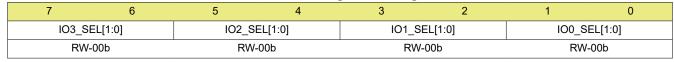

TMP1827 是一款高精度、单线兼容的数字输出温度传 感器,集成了 2kbit EEPROM 和 SHA-256-HMAC 认 证方案,具有从 - 55°C 到 +150°C 的宽工作温度范 围。TMP1827 在 - 20°C 至 +85°C 的温度范围内提供 ±0.1°C(典型值)/±0.3°C(最大值)的高精度。每个 器件都带有一个工厂编程的 64 位唯一标识号,用于寻 址和 NIST 可追溯性。TMP1827 支持传统应用的标准 速度和具有 90kbps 数据速率的过载模式,可在 1.7V 至 5.5V 的宽电压范围内实现低延迟通信。

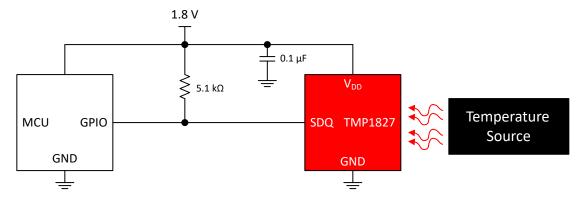

在最简单的运行模式下,TMP1827单线接口在数据引 脚上集成了 8kV IEC-61000-4-2 ESD 保护, 在总线供 电模式下只需要一个连接和一个接地回路,从而通过减 少电线和外部保护元件的数量来降低成本。此外, V<sub>DD</sub> 电源引脚还可用于可能需要专用电源的应用。

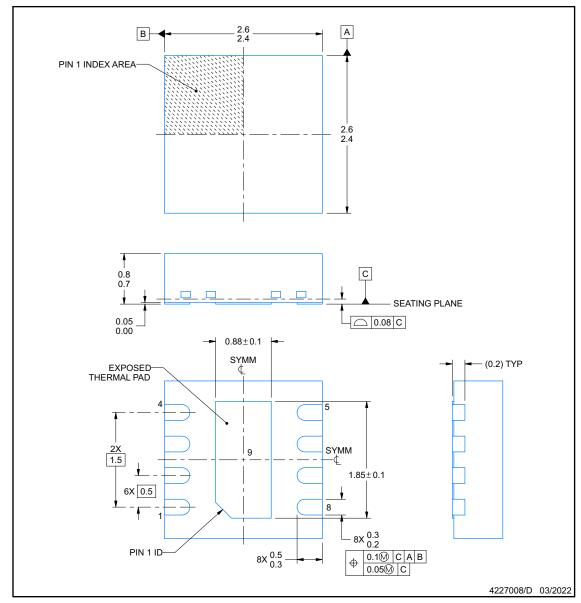

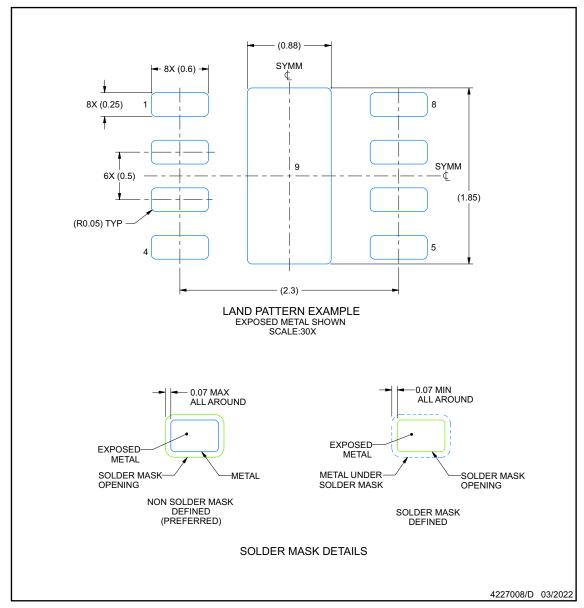

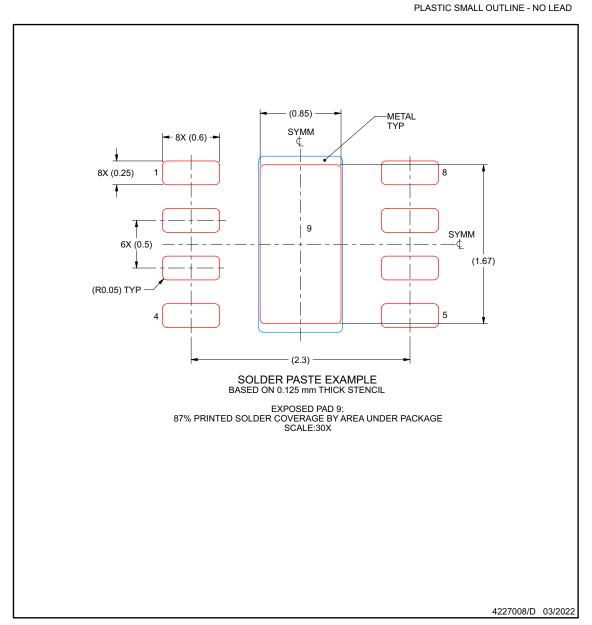

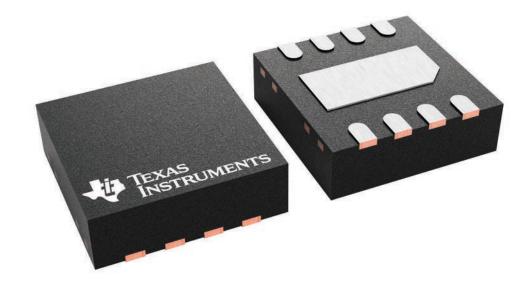

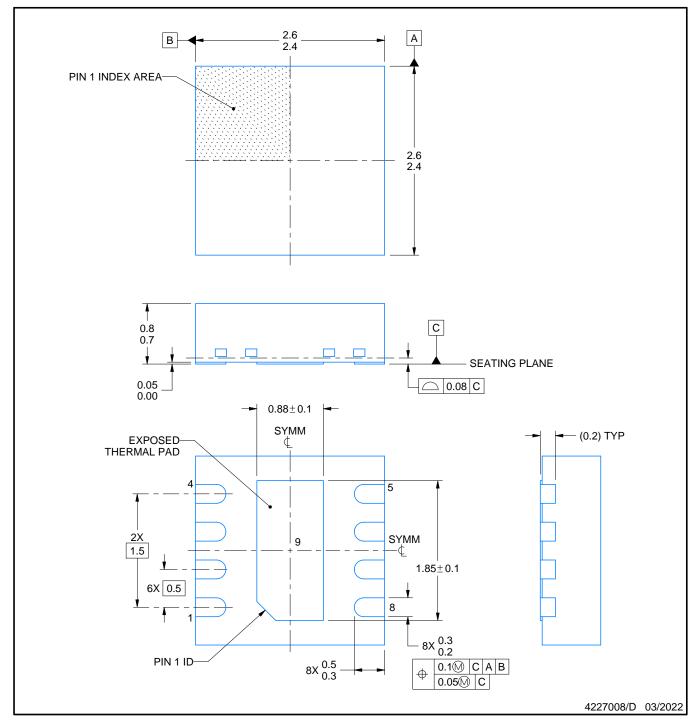

# 封装信息

| 器件型号    | 封装 <sup>(1)</sup> | 封装尺寸(标称值)       |  |  |

|---------|-------------------|-----------------|--|--|

| TMP1827 | WSON (8)          | 2.50mm × 2.50mm |  |  |

有关所有的可用封装,请参阅数据表末尾的可订购产品附录。

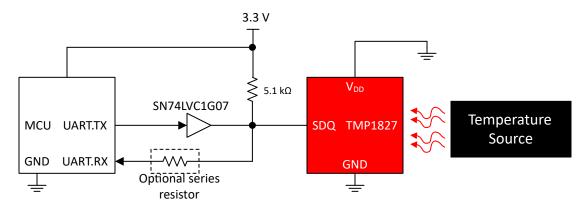

简化原理图

# **Table of Contents**

| 1 特性                                 | 1 | 8.3 Feature Description                 | 13               |

|--------------------------------------|---|-----------------------------------------|------------------|

| 2 应用                                 |   | 8.4 Device Functional Modes             |                  |

|                                      |   | 8.5 Programming                         | 39               |

| 4 Revision History                   |   | 8.6 Register Maps                       |                  |

| 5 说明(续)                              |   | 9 Application and Implementation        | <mark>55</mark>  |

| 6 Pin Configuration and Functions    |   | 9.1 Application Information             | 55               |

| 7 Specifications                     |   | 9.2 Typical Applications                | 55               |

| 7.1 Absolute Maximum Ratings         |   | 9.3 Power Supply Recommendations        | <mark>58</mark>  |

| 7.2 ESD Ratings                      |   | 9.4 Layout                              | <u>5</u> 8       |

| 7.3 Recommended Operating Conditions |   | 10 Device and Documentation Support     | 59               |

| 7.4 Thermal Information              |   | 10.1 Documentation Support              | <mark>5</mark> 9 |

| 7.5 Electrical Characteristics       |   | 10.2 接收文档更新通知                           | <mark>5</mark> 9 |

| 7.6 1-Wire Interface Timing          |   | 10.3 支持资源                               | <mark>5</mark> 9 |

| 7.7 Security Engine Characteristics  |   | 10.4 Trademarks                         | 59               |

| 7.8 EEPROM Characteristics           |   | 10.5 Electrostatic Discharge Caution    | <mark>5</mark> 9 |

| 7.9 Timing Diagrams                  |   | 10.6 术语表                                |                  |

| 7.10 Typical Characteristics         |   | 11 Mechanical, Packaging, and Orderable |                  |

| 8 Detailed Description               |   | Information                             | 59               |

| 8.1 Overview                         |   | 11.1 Package Option Addendum            | 63               |

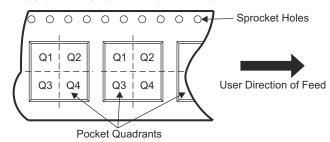

| 8.2 Functional Block Diagram         |   | 11.2 Tape and Reel Information          |                  |

| 3                                    |   | ·                                       |                  |

4 Revision History 注:以前版本的页码可能与当前版本的页码不同

| DATE           | REVISION | NOTES           |

|----------------|----------|-----------------|

| September 2022 | *        | Initial Release |

Submit Document Feedback

# 5 说明(续)

TMP1827 实施 SHA-256-HMAC 身份验证引擎以及密钥存储,以满足终端设备的系统身份验证要求。器件上的 2 kbit EEPROM 允许主机应用以 64 位块大小存储应用特定的内容。存储器能以 256 位的页面大小进行写保护,以避免意外的数据覆盖。存储器架构使应用能够在更新只有几个字节的变量时优化总线带宽,同时为写保护提供理想存储器大小。该器件还具有通过经过身份验证的存储器写入操作进行主机身份验证的机制。

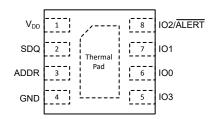

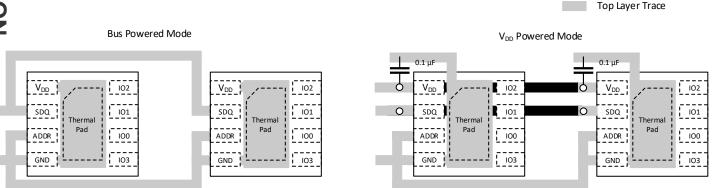

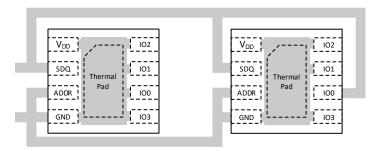

# **6 Pin Configuration and Functions**

图 6-1. NGR 8-Pin WSON Top View

表 6-1. Pin Functions

| PI                                                                                                    | IN        | I/O                                                                                           | DESCRIPTION                                                                                                        |

|-------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                  | WSON      | 1/0                                                                                           |                                                                                                                    |

| ADDR                                                                                                  | 3         | 1                                                                                             | Resistor address select. If unused, TI recommends to connect pin to ground                                         |

| GND 4 — Ground                                                                                        |           | Ground                                                                                        |                                                                                                                    |

| 100                                                                                                   | 100 6 I/O |                                                                                               | General-purpose digital IO. If unused, TI recommends to connect pin to ground                                      |

| IO1                                                                                                   | 7         | I/O                                                                                           | General-purpose digital IO. If unused, TI recommends to connect pin to ground                                      |

| IO2/ALERT                                                                                             | 8         | I/O                                                                                           | General-purpose digital IO or configurable as temperature alert. If unused, TI recommends to connect pin to ground |

| IO3                                                                                                   | 5         | I/O                                                                                           | General-purpose digital IO. If unused, TI recommends to connect pin to ground                                      |

| SDQ 2 I/O Serial bidirectional data. In bus power mode, the pin is used to power the internal capacit |           | Serial bidirectional data. In bus power mode, the pin is used to power the internal capacitor |                                                                                                                    |

| $V_{DD}$                                                                                              | 1         | 1                                                                                             | Supply voltage in V <sub>DD</sub> powered mode. In bus powered mode, must be connected to ground                   |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

Over free-air temperature range unless otherwise noted<sup>(1)</sup>

|                       |                           | MIN   | MAX                   | UNIT |

|-----------------------|---------------------------|-------|-----------------------|------|

| Supply voltage        | $V_{DD}$                  |       | 6.5                   | V    |

| I/O voltage           | SDQ, Bus powered mode     | - 0.3 | 6.5                   | V    |

| 70 voltage            | SDQ, Supply powered mode  | - 0.3 | V <sub>DD</sub> + 0.3 | V    |

| I/O voltage           | IO0, IO1, IO2, IO3        | - 0.3 | 6.5                   | V    |

| I/O voltage           | ADDR                      | - 0.3 | 1.65                  | V    |

| Operating junction te | mperature, T <sub>J</sub> | - 55  | 155                   | °C   |

| Storage temperature   | , T <sub>stg</sub>        | - 65  | 155                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                                  |                                                                   |                                                                                |          |       | UNIT |

|----------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------|----------|-------|------|

| V <sub>(ESD)</sub> Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | All pins                                                                       | ±2000    | V     |      |

|                                  | Electrostatic<br>discharge                                        | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | All pins | ±500  | V    |

|                                  | 3                                                                 | IEC 61000-4-2 Contact Discharge                                                | SDQ pin  | ±8000 | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

|                  |                                                                                   | MIN  | NOM MAX               | UNIT |

|------------------|-----------------------------------------------------------------------------------|------|-----------------------|------|

| $V_{DD}$         | Supply voltage V <sub>DD</sub> powered mode                                       | 1.70 | 5.5                   | V    |

| V <sub>PUR</sub> | Supply voltage on SDQ in bus powered mode (V <sub>DD</sub> = GND)                 | 1.70 | 5.5                   | V    |

| V                | All IO pins in V <sub>DD</sub> powered mode (except SDQ and ADDR <sup>(1)</sup> ) | 0    | 5.5                   | V    |

| V <sub>I/O</sub> | SDQ pin in V <sub>DD</sub> powered mode                                           | 0    | V <sub>DD</sub> + 0.3 | V    |

| T <sub>A</sub>   | Operating ambient temperature <sup>(2)</sup>                                      | -55  | 150                   | °C   |

<sup>(1)</sup> If ADDR pin is not used, it is recommended to be connected to GND

### 7.4 Thermal Information

|                        |                                              | TMP1827    |       |

|------------------------|----------------------------------------------|------------|-------|

|                        | THERMAL METRIC(1)                            | NGR (WSON) | UNIT  |

|                        |                                              | 8 PINS     |       |

| R <sub> θ JA</sub>     | Junction-to-ambient thermal resistance       | 66.1       | °C/W  |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 55.7       | °C/W  |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 20.2       | °C/W  |

| R <sub> θ JB</sub>     | Junction-to-board thermal resistance         | 26.3       | °C/W  |

| ψJT                    | Junction-to-top characterization parameter   | 1.0        | °C/W  |

| ψ ЈВ                   | Junction-to-board characterization parameter | 26.1       | °C/W  |

| M <sub>T</sub>         | Thermal Mass                                 | TBD        | mJ/°C |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

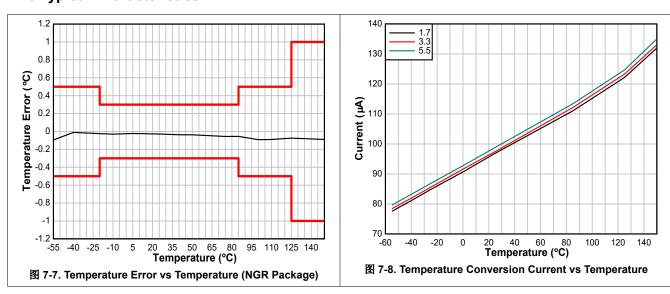

### 7.5 Electrical Characteristics

Over free-air temperature range and  $V_{DD}$  = 1.7 V to 5.5 V (unless otherwise noted); Typical specifications are at  $T_A$  = 25 °C and  $V_{DD}$  = 3.3 V (unless otherwise noted)

|                     | PARAMETER                          | TEST CO                                                                                                                              | NDITIONS                                                                              | MIN | TYP    | MAX   | UNIT |

|---------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----|--------|-------|------|

| TEMPERA             | ATURE SENSOR                       |                                                                                                                                      |                                                                                       |     |        |       |      |

|                     |                                    | - 20 °C to 85°C                                                                                                                      |                                                                                       |     | ±0.1   | ±0.3  |      |

| T <sub>ERR</sub>    | Temperature accuracy               | - 55 °C to 125°C                                                                                                                     |                                                                                       |     | ±0.3   | ±0.5  | °C   |

|                     |                                    | - 55 °C to 150°C                                                                                                                     |                                                                                       |     | ±0.5   | ±1.0  |      |

| PSR                 | DC power supply sensitivity        |                                                                                                                                      |                                                                                       |     |        | ±0.03 | °C/V |

| т                   | Temperature resolution             | Including sign bit                                                                                                                   |                                                                                       | 16  |        | Bits  |      |

| T <sub>RES</sub>    | remperature resolution             | LSB 7.8125                                                                                                                           |                                                                                       | m°C |        |       |      |

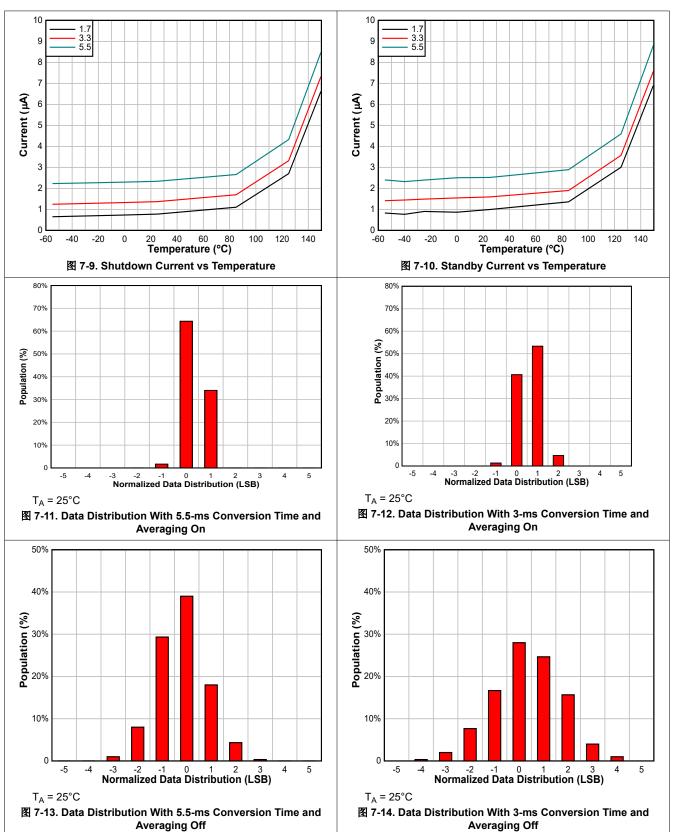

| T <sub>REPEAT</sub> | Repeatability <sup>(1)</sup>       | V <sub>DD</sub> = 3.3 V<br>Averaging enabled, Conversion Time = 5.5 ms,<br>16-bit mode,<br>1-Hz conversion interval, 300 acquisition |                                                                                       |     | ±2     |       | LSB  |

| T <sub>LTD</sub>    | Long-term stability and drift      | 1000 hours at 150°C <sup>(2)</sup>                                                                                                   |                                                                                       |     | 0.0625 |       | °C   |

| T <sub>HYST</sub>   | Temperature cycling and hysteresis | $T_{START} = -40^{\circ}C$<br>$T_{FINISH} = 150^{\circ}C$<br>$T_{TEST} = 25^{\circ}C$<br>3 cycles                                    | T <sub>START</sub> = -40°C<br>T <sub>FINISH</sub> = 150°C<br>T <sub>TEST</sub> = 25°C |     | 4      |       | LSB  |

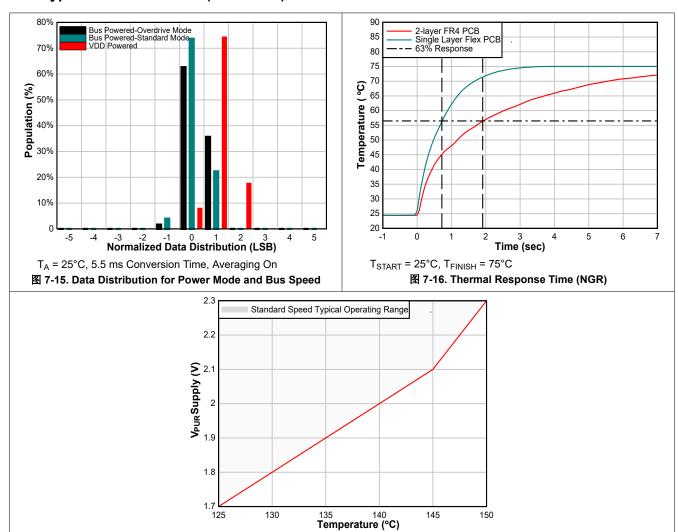

|                     | Response time (Stirred             | Single layer Flex PCB                                                                                                                | - τ = 63 %                                                                            |     | 0.77   |       | s    |

| t <sub>RESP_L</sub> | Liquid)                            | 2-layer 62-mil Rigid<br>PCB                                                                                                          | 25°C to 75°C                                                                          |     | 1.91   |       | s    |

| •                   | Active Conversion time (No         | CONV_TIME_SEL = 0                                                                                                                    | (图 8-12)                                                                              | TBD | 3      | TBD   | ms   |

| t <sub>ACT</sub>    | Averaging)                         | CONV_TIME_SEL = 1                                                                                                                    |                                                                                       | TBD | 5.5    | TBD   | ms   |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

<sup>(2)</sup> In bus powered mode, overdrive speed supports the max operating temperature up to 150°C, while standard speed supports up to 125°C for full V<sub>PUR</sub> range and 150C for V<sub>PUR</sub> > 2.5V (See <a>[X]</a> 7-17)

Over free-air temperature range and  $V_{DD}$  = 1.7 V to 5.5 V (unless otherwise noted); Typical specifications are at  $T_A$  = 25 °C and  $V_{DD}$  = 3.3 V (unless otherwise noted)

|                        | PARAMETER                                                            | TEST CO                                       | NDITIONS                                                                                               | MIN                  | TYP   | MAX                  | UNIT       |

|------------------------|----------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------|-------|----------------------|------------|

| t <sub>DELAY</sub>     | Start-up delay for temperature conversion and EEPROM programming     |                                               |                                                                                                        | 100                  |       | 300                  | μs         |

| SDQ DIGIT              | AL INPUT/OUTPUT                                                      |                                               |                                                                                                        | ,                    |       |                      |            |

| C <sub>IN</sub>        | SDQ pin capacitance                                                  |                                               |                                                                                                        |                      | 40    |                      | pF         |

| V <sub>IL</sub>        | Input logic low level <sup>(3)</sup>                                 |                                               |                                                                                                        | - 0.3                |       | 0.2 × V <sub>S</sub> | V          |

| V <sub>IH</sub>        | Input logic high level <sup>(3)</sup>                                |                                               |                                                                                                        | 0.8 × V <sub>S</sub> |       | V <sub>S</sub> + 0.3 | V          |

| V <sub>HYST</sub>      | Hysteresis                                                           |                                               |                                                                                                        |                      | 0.3   |                      | V          |

| I <sub>IN</sub>        | Input leakage current                                                |                                               |                                                                                                        |                      | ±0.5  | TBD                  | μА         |

| V <sub>OL</sub>        | Output low level                                                     | I <sub>OL</sub> = -4 mA                       |                                                                                                        |                      |       | 0.4                  | V          |

| GPIO CHA               | RACTERISTICS                                                         | 1                                             |                                                                                                        |                      |       |                      |            |

| C <sub>IN</sub>        | Input capacitance                                                    |                                               |                                                                                                        |                      | 10    |                      | pF         |

| V <sub>IL</sub>        | Input logic low level <sup>(3)</sup>                                 |                                               |                                                                                                        | - 0.3                |       | 0.2 × V <sub>S</sub> | V          |

| V <sub>IH</sub>        | Input logic high level <sup>(3)</sup>                                |                                               |                                                                                                        | 0.8 × V <sub>S</sub> |       | V <sub>S</sub> + 0.3 | V          |

| I <sub>IN</sub>        | Input leakage current                                                |                                               |                                                                                                        |                      | 0     | ±0.1                 | μA         |

| $V_{HYST}$             | Hysteresis                                                           |                                               |                                                                                                        |                      | 0.175 |                      | V          |

| $V_{OL}$               | Output low level                                                     | I <sub>OL</sub> = -4 mA                       |                                                                                                        |                      |       | 0.4                  | V          |

| RESISTOR               | ADDRESS DECODER CHARA                                                | CTERISTICS                                    |                                                                                                        |                      |       |                      | •          |

| C <sub>LOAD</sub>      | Load capacitance as seen on<br>ADDR pin (includes PCB<br>parasitics) |                                               |                                                                                                        |                      |       | 100                  | pF         |

|                        | R <sub>ADDR</sub> resistor range                                     |                                               |                                                                                                        | 6.49                 |       | 54.9                 | kΩ         |

|                        | R <sub>ADDR</sub> resistor tolerance                                 | T <sub>A</sub> = 25°C                         |                                                                                                        | - 1.0                |       | 1.0                  | %          |

|                        | R <sub>ADDR</sub> resistor temperature coefficient                   |                                               |                                                                                                        | - 100                |       | 100                  | ppm/°C     |

|                        | R <sub>ADDR</sub> resistor lifetime drift                            |                                               |                                                                                                        | - 0.2                |       | 0.2                  | %          |

| t <sub>RESDET</sub>    | Resistor decoding time                                               |                                               |                                                                                                        |                      | 2.8   |                      | ms         |

| POWER SI               | JPPLY                                                                |                                               |                                                                                                        |                      |       |                      |            |

| I <sub>PU</sub>        | Pullup current <sup>(4)</sup>                                        | Bus powered mode, seria                       | al bus inactive                                                                                        | 300                  |       |                      | μA         |

| I <sub>DD_ACTIVE</sub> | Supply current during temperature conversion                         | Temperature Conversion                        | , serial bus inactive                                                                                  |                      | 97    | TBD                  | μА         |

|                        |                                                                      | V <sub>DD</sub> powered, serial bus           | T <sub>A</sub> = -55°C to 85°C                                                                         |                      | 1.59  | TBD                  |            |

| I <sub>DD_SB</sub>     | Standby current <sup>(5)</sup>                                       | inactive, continous conversion mode           | T <sub>A</sub> = -55°C to 150°C                                                                        |                      |       | TBD                  | μ <b>A</b> |

| $I_{DD\_SD}$           | Shutdown current                                                     | Serial bus inactive, one shot conversion mode | $T_A = -55^{\circ}\text{C to } 85^{\circ}\text{C}$ $T_A = -55^{\circ}\text{C to } 150^{\circ}\text{C}$ |                      | 1.01  | TBD<br>TBD           | μ <b>А</b> |

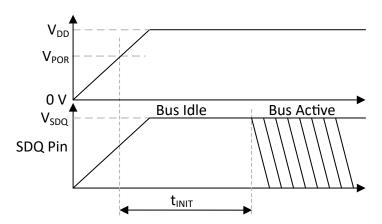

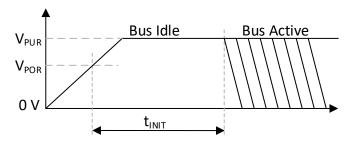

| V <sub>POR</sub>       | Power-on reset threshold voltage                                     | Supply rising (图 7-4, 图                       |                                                                                                        | 1.5                  |       |                      | ٧          |

| FUR                    | Brownout detect                                                      | Supply falling                                |                                                                                                        |                      |       | 1.3                  | V          |

| t <sub>INIT</sub>      | Reset Initialization Time                                            | Time required by device (图 7-4, 图 7-5)        | to reset after power up                                                                                |                      |       | 2.0                  | ms         |

- (1) Repeatability is the ability to reproduce a reading when the measured temperature is applied consecutively, under the same conditions.

- (2) Long term stability is determined using accelerated operational life testing at a junction temperature of 150°C.

- (3) In bus powered mode  $V_S = V_{PUR}$ . In supply powered mode  $V_S = V_{DD}$ .

- (4) The pullup current parameter is required to size the bus pullup resistor (See † 8.3.3) for active temperature conversion or EEPROM read and program or authentication operations.

- (5) Quiescent current between conversions.

Submit Document Feedback

### 7.6 1-Wire Interface Timing

Over free-air temperature range and  $V_{DD}$  = 1.70 V to 5.5 V (unless otherwise noted)

|                    |                                                                        | STANDARD                         | MODE                                  | OVERDRIVE MODE                   |                                  | UNIT |

|--------------------|------------------------------------------------------------------------|----------------------------------|---------------------------------------|----------------------------------|----------------------------------|------|

|                    |                                                                        | MIN                              | MAX                                   | MIN                              | MAX                              | UNII |

| BUS RESET          | AND BIT SLOT TIMING                                                    |                                  | ,                                     |                                  | '                                |      |

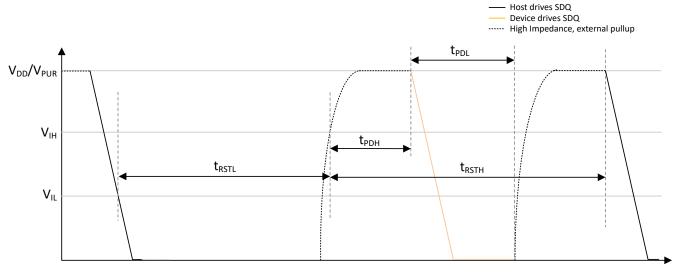

| t <sub>RSTL</sub>  | Host to device bus reset pulse width (图 7-1) <sup>(1)</sup>            | 480                              | 560                                   | 48                               | 80                               | μs   |

| t <sub>RSTH</sub>  | Device to host response time (图 7-1) <sup>(2)</sup>                    | 480                              |                                       | 48                               |                                  | μs   |

| t <sub>PDH</sub>   | Device turnaround time for bus reset response (图 7-1)                  | 15                               | 60                                    | 2                                | 8                                | μs   |

| t <sub>PDL</sub>   | Device to host response pulse width (图 7-1)                            | 60                               | 240                                   | 8                                | 24                               | μs   |

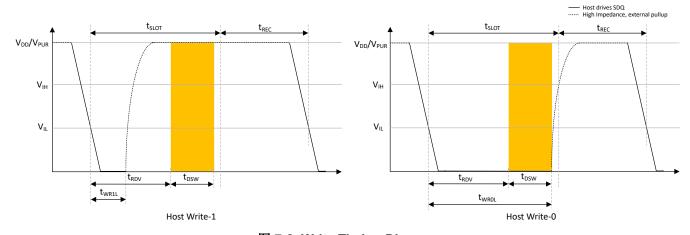

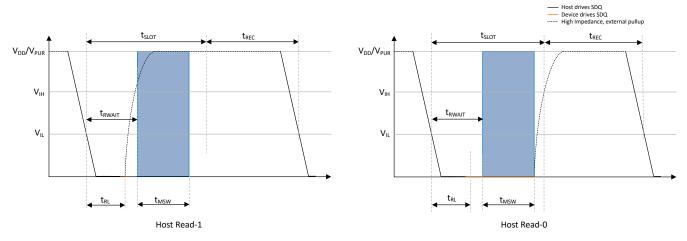

| t <sub>SLOT</sub>  | Bit slot time (图 7-2, 图 7-3)                                           | 60                               | 120                                   | 11                               |                                  | μs   |

| t <sub>REC</sub>   | Recovery time (图 7-2, 图 7-3)                                           | 2                                |                                       | 2                                |                                  | μs   |

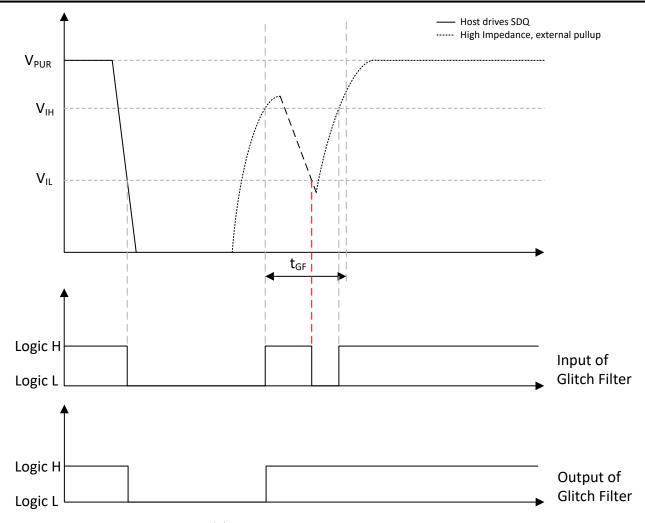

| t <sub>GF</sub>    | Glitch filter width (图 7-6) <sup>(3)</sup>                             | 0.48                             |                                       | 0.025                            |                                  | μs   |

| t <sub>F</sub>     | Fall time                                                              |                                  | 100                                   |                                  | 100                              | ns   |

| BIT WRITE          | TIMING                                                                 |                                  | •                                     |                                  |                                  |      |

| t <sub>WR0L</sub>  | Host write 0 width (图 7-2)                                             | 60                               | 120                                   | 9                                | 10                               | μs   |

| t <sub>WR1L</sub>  | Host write 1 width (图 7-2)                                             | 2                                | 15                                    | 1                                | 2                                | μs   |

| t <sub>RDV</sub>   | Device read data valid time (图 7-2)                                    | 15                               |                                       | 2                                |                                  | μs   |

| t <sub>DSW</sub>   | Device read data window (图 7-2)                                        | 15                               | 45                                    | 2                                | 7                                | μs   |

| BIT READ T         | IMING                                                                  |                                  | · · · · · · · · · · · · · · · · · · · |                                  |                                  |      |

| t <sub>RL</sub>    | Host drive read bit slot time (图 7-3)                                  | 2                                | 5                                     | 2                                | 3                                | μs   |

| t <sub>RWAIT</sub> | Host wait time before read data sampling window (图 7-3) <sup>(4)</sup> |                                  | t <sub>RL</sub> +t <sub>RC</sub>      |                                  | t <sub>RL</sub> +t <sub>RC</sub> | μs   |

| t <sub>MSW</sub>   | Host read data sampling window (图 7-3)                                 | t <sub>RL</sub> +t <sub>RC</sub> | 30                                    | t <sub>RL</sub> +t <sub>RC</sub> | 3                                | μs   |

- (1) In bus powered mode, extending the t<sub>RSTL</sub> above 600 µs may cause the device to power on reset

- (2) The t<sub>RSTH</sub> is the maximum time the host must wait to receive a response from the furthest device, taking into account the propagation delay and recovery time for all the devices.

- (3) The glitch filter timing applies only on the rising edge of the SDQ signal

- (4) The t<sub>RC</sub> time is defined as the time taken for the bus voltage to rise from 0V to minimum V<sub>IH</sub> of the host. This is a function of the bus pullup resistor and parasitic capcitance of the trace or cable.

# 7.7 Security Engine Characteristics

Over free-air temperature range and  $V_{DD}$  = 1.7 V to 5.5 V (unless otherwise noted)

|                           |                                                                        | MIN | TYP | MAX | UNIT |

|---------------------------|------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>HASH_DATA</sub>    | Computation time for SHA-256 hash calculation for data size of 8 bytes |     |     | 355 | μs   |

| t <sub>DECOMMISSION</sub> | Time for decommission of the device                                    |     | 78  | 130 | ms   |

| I <sub>DD_HASH</sub>      | Hash computation current                                               |     |     | TBD | μΑ   |

#### 7.8 EEPROM Characteristics

Over free-air temperature range and  $V_{DD}$  = 1.7 V to 5.5 V (unless otherwise noted); Typical specifications are at  $T_A$  = 25°C and  $V_{DD}$  = 3.3 V (unless otherwise noted)

|                       |                                                      | MIN | TYP  | MAX | UNIT  |

|-----------------------|------------------------------------------------------|-----|------|-----|-------|

|                       | Programming time for 8-byte data word in user EEPROM |     | 13.2 | 21  | ms    |

| PROG                  | Programming time for register copy to EEPROM         |     | 26.4 | 42  | ms    |

| t <sub>READIDLE</sub> | Idle bus time for EEPROM 8-byte data word fetch      |     |      | 400 | μs    |

| I <sub>DD_PROG</sub>  | Programming current                                  |     | 178  | TBD | μΑ    |

| Data Retention        | at T <sub>A</sub> = 125°C                            | 25  |      |     | years |

|                       | at T <sub>A</sub> = 150°C                            | 10  |      |     | years |

Over free-air temperature range and  $V_{DD}$  = 1.7 V to 5.5 V (unless otherwise noted); Typical specifications are at  $T_A$  = 25°C and  $V_{DD}$  = 3.3 V (unless otherwise noted)

|           |                              | MIN  | TYP   | MAX | UNIT   |

|-----------|------------------------------|------|-------|-----|--------|

| Endurance | For erase and program cycles | 1000 | 20000 |     | cycles |

# 7.9 Timing Diagrams

图 7-1. Bus Reset Timing Diagram

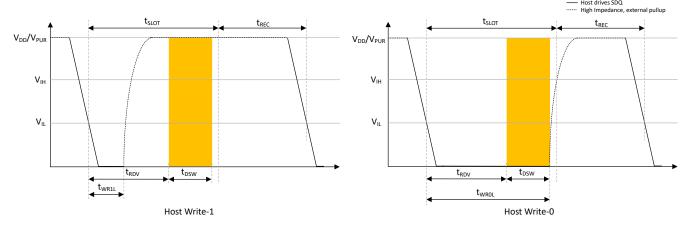

图 7-2. Write Timing Diagram

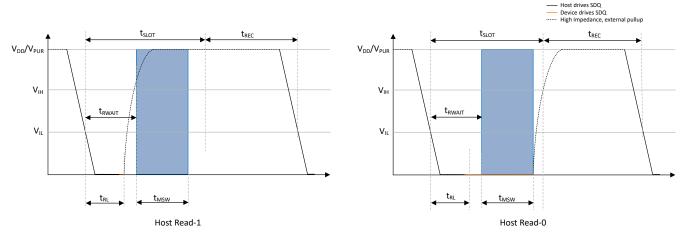

图 7-3. Read Timing Diagram

图 7-4.  $V_{DD}$  Powered Initialization Timing Diagram

图 7-5. Bus Powered Initialization Timing Diagram

图 7-6. Glitch Filter Timing Diagram

# 7.10 Typical Characteristics

Submit Document Feedback

# 7.10 Typical Characteristics (continued)

# 7.10 Typical Characteristics (continued)

图 7-17. V<sub>PUR</sub> Minimum Supply Voltage vs Temperature (Standard Speed)

# 8 Detailed Description

### 8.1 Overview

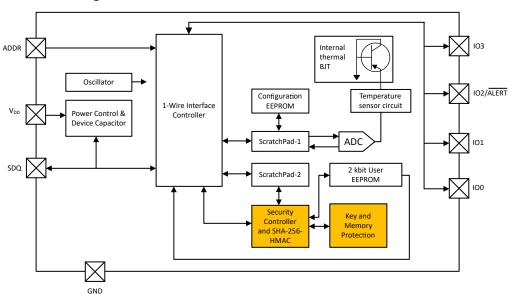

The TMP1827 is a digital output temperature sensor designed for thermal-management and thermal-protection applications. The TMP1827 is a single-wire device which can operate in either supply powered or bus powered (parasitic powered) mode. The device features a 2-kbit EEPROM, SHA-256-HMAC based authentication engine. 8-1 shows a block diagram of the TMP1827.

# 8.2 Functional Block Diagram

图 8-1. Functional Block Diagram

### 8.3 Feature Description

#### 8.3.1 Power Up

The device operates in both supply powered and bus powered mode. Irrespective of the mode, when the supply voltage reaches within the operating range, the device requires  $t_{\text{INIT}}$  to initialize itself. After  $t_{\text{INIT}}$ , the host MCU can begin accessing the device.

During initialization, the device may not respond to any bus activity. When initialization is complete, the device shall wait for the bus reset from the host. During the initialization for the device, the following events take place:

- The EEPROM content for short address, temperature alert low, temperature alert high and temperature offset registers are restored.

- The EEPROM for the IO configuration register is read and contents of the IO configuration register is restored.

- The EEPROM content for device configuration-1 and device configuration-2 registers are restored to the respective registers.

- If the ARB\_MODE bits are set to value other than '00b', then the device will respond to the SEARCHADDR in arbitration mode.

- If OD\_EN bit is set to '1b', then the device shall communicate in overdrive speed, unless the first bus reset pulse from the host is sent in standard speed.

- The user memory protection bits are restored and appropriate protection to the user EEPROM block applied.

- The authentication key and secret bytes are read from the EEPROM to internal flops for the authentication operation.

#### 8.3.2 Power Mode Switch

The device is designed to operate in supply powered or bus powered mode. The dual mode implementation provides a unique method of redundancy that, even in cases where the power supply pin gets disconnected, the device can draw power from data pin, as long as the pullup resistor value used is as per the specification limit. This may be the system case where while operating in supply powered mode, the supply pin may accidentally get disconnected, especially under harsh operating conditions.

When the device switches from supply powered to bus powered mode, the device shall operate with the same settings until the internal capacitor is able to provide the current draw required by the device for communication and the external pullup resistor can charge the internal capacitor during bus idle time. If the internal voltage on the capacitor drops below the brown-out threshold, the device shall switch itself off and enter bus powered mode of communication on subsequent power up. The device may not complete the ongoing communication during this time. When the device completes the power-up initialization sequence, as described earlier, the device shall respond to first bus communication starting with the bus reset sequence.

#### 8.3.3 Bus Pullup Resistor

The bus pullup resistance value selected is important for communication as per the speed mode and ensuring that minimal possible energy is consumed in the application. If the resistor value is too small, it may violate the V<sub>OL</sub> limits on the SDQ pin.

The total SDQ pin and bus capacitance must be considered along with the bus leakage current when selecting the pullup resistor. The pullup resistance value selected must also ensure that the signal level reaches V<sub>IH</sub> as per the timing requirements for standard and overdrive mode.

In bus powered mode of operation, the device charges its internal capacitor through the SDQ pin and the pullup resistor. This charge on the capacitor is used during bus communication, when the SDQ pin low. For other high current functions like thermal conversion and EEPROM access, the bus is held idle to ensure that the device can draw current through the pullup resistor. The SDQ pin voltage during the high current operation must be maintained to ensure sufficient operating margins. Use 方程式 1 to calculate the pullup resistor value.

$$\frac{\left(V_{PUR} - V_{OL(MAX)}\right)}{4 \times 10^{-3}} < R_{PUR} < \frac{\left(V_{PUR} - 1.6\right)}{I_{PU(MIN)}} \tag{1}$$

When the device is used in V<sub>DD</sub> or supply powered mode, a larger pullup resistor value may be used, as the SDQ pin is used only for communication. The user must ensure that the pullup resistor value selected must be able to support the timing for the required bus speed of operation.

For low current consumption devices like TMP1827, selecting the correct pullup resistor value allows the application to avoid low impedance current path components for bus powered mode of operation while maintaining communication speeds and device parameters as per its electrical specification.

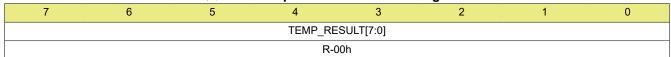

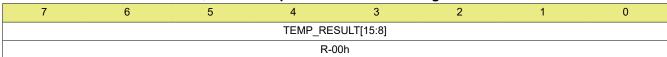

### 8.3.4 Temperature Results

The conversion is initiated by the host MCU by sending the temperature conversion command if the automatic conversion is disabled, or immediately after the presence detect is completed when the automatic conversion is enabled, or in continuous conversion mode if the device is V<sub>DD</sub> powered. At the end of every conversion, the device updates the temperature registers temperature result and the status register bits.

8 8-2 shows that the device supports a high precision and legacy format, which can be configured through the TEMP FMT bit in the device configuration-1 register.

Product Folder Links: TMP1827

Submit Document Feedback

| Temperature Result MSB Register |                       |                |                       |                |                |                |                | Ter            | mperature Re    | sult LSB Regis  | ster            |                 |                 |                 |                 |

|---------------------------------|-----------------------|----------------|-----------------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| High Pred                       | High Precision Format |                |                       |                |                |                |                |                |                 |                 |                 |                 |                 |                 |                 |

| S                               | 2 <sup>7</sup>        | 2 <sup>6</sup> | <b>2</b> <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> | 2 <sup>-1</sup> | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 2 <sup>-4</sup> | 2 <sup>-5</sup> | 2 <sup>-6</sup> | 2 <sup>-7</sup> |

| Legacy Format                   |                       |                |                       |                |                |                |                |                |                 |                 |                 |                 |                 |                 |                 |

| S                               | S                     | S              | S                     | S              | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup>  | 2 <sup>1</sup>  | 2 <sup>0</sup>  | 2 <sup>-1</sup> | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 2 <sup>-4</sup> |

图 8-2. Temperature Format

If the format selected is the high precision 16-bit format, the data in the result registers is stored in two's complement form and has a resolution of  $0.0078125^{\circ}$ C. If the format selected is the legacy 12-bit format, the data in the result register is stored in sign extended form and has a resolution of  $0.0625^{\circ}$ C. The temperature register reads as  $0^{\circ}$ C before the first conversion.  $\frac{1}{8}$  8-1 and  $\frac{1}{8}$  8-2 show examples of possible binary data that can be read from the temperature result registers and the corresponding hexadecimal and temperature equivalents for both formats.

表 8-1. Precision (16-Bit) Temperature Data Format

| TEMPERATURE | DIGITAL OUTPUT (P   | RECISION FORMAT) |

|-------------|---------------------|------------------|

| (°C)        | BINARY              | HEXADECIMAL      |

| 150         | 0100 1011 0000 0000 | 4B00             |

| 127         | 0011 1111 1000 0000 | 3F80             |

| 100         | 0011 0010 0000 0000 | 3200             |

| 25          | 0000 1100 1000 0000 | 0C80             |

| 1           | 0000 0000 1000 0000 | 0080             |

| 0.125       | 0000 0000 0001 0000 | 0010             |

| 0.03125     | 0000 0000 0000 0100 | 0004             |

| 0.0078125   | 0000 0000 0000 0001 | 0001             |

| 0           | 0000 0000 0000 0000 | 0000             |

| - 0.0078125 | 1111 1111 1111 1111 | FFFF             |

| - 0.03125   | 1111 1111 1111 1100 | FFFC             |

| - 0.125     | 1111 1111 1111 0000 | FFF0             |

| - 1         | 1111 1111 1000 0000 | FF80             |

| - 25        | 1111 0011 1000 0000 | F380             |

| - 40        | 1110 1100 0000 0000 | FC00             |

| - 55        | 1110 0100 1000 0000 | F480             |

表 8-2. Legacy (12-Bit) Temperature Data Format

| TEMPERATURE | DIGITA              | L OUTPUT    |

|-------------|---------------------|-------------|

| (°C)        | BINARY              | HEXADECIMAL |

| 128         | 0000 0111 1111 1111 | 07FF        |

| 127.9375    | 0000 0111 1111 1111 | 07FF        |

| 100         | 0000 0110 0100 0000 | 0640        |

| 25          | 0000 0001 1001 0000 | 0190        |

| 1           | 0000 0000 0001 0000 | 0010        |

| 0.125       | 0000 0000 0000 0010 | 0002        |

| 0           | 0000 0000 0000 0000 | 0000        |

| - 0.125     | 1111 1111 1111 1110 | FFFE        |

| - 1         | 1111 1111 1111 0000 | FFF0        |

| - 25        | 1111 1110 0111 0000 | FE70        |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

| 表 8-2. Legacy | (12-Bit)   | Temperature    | Data Forn    | nat (continued) |

|---------------|------------|----------------|--------------|-----------------|

| 1 U-Z. LEGACY | (   4-0 () | i ciliperature | , Dala i Oii | nat (Continued) |

| TEMPERATURE | DIGITAL             | OUTPUT      |

|-------------|---------------------|-------------|

| (°C)        | BINARY              | HEXADECIMAL |

| - 40        | 1111 1101 1000 0000 | FD80        |

| - 55        | 1111 1100 1001 0000 | FC90        |

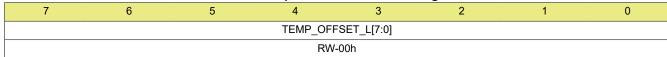

#### 8.3.5 Temperature Offset

The temperature offset has the same format as the temperature result and is stored in the temperature offset registers.

The device, after every temperature conversion, shall apply the offset value before the temperature is stored in the temperature result register. The host write to the registers can be stored in the configuration EEPROM of the device, thereby reducing the overhead as the host does not need to reprogram the values at every power up. The offset features allow the device to achieve better accuracy at the temperature range for the application by performing a single point calibration.

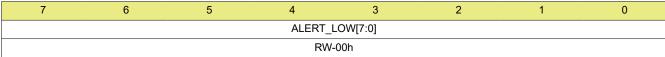

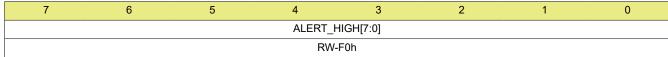

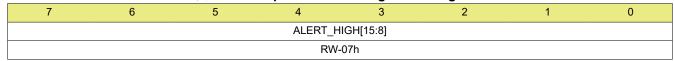

#### 8.3.6 Temperature Alert

The temperature alert feature uses the temperature alert low registers for low threshold comparison and temperature alert high registers for high threshold comparison. The format of the register is the same as the temperature results.

The device shall compare the result of the last conversion with the alert thresholds. If the temperature result is less than the low limit, or more than the high limits, then the device shall set the appropriate alert status flag for low or high temperature limits, in the status register. The alert status flags are cleared based on the ALERT MODE setting in the device configuration-1 register.

Additionally, if the IO2/ALERT pin is configured as an alert pin, the alert status is reflected on the pin.

#### 8.3.7 Standard Device Address

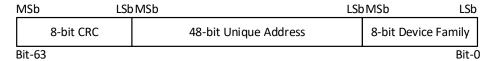

Every device comes with a unique 64-bit address that is factory programmed. Additionally the device provides flexible addressing modes that the host controller may use to improve bus throughput. This is described below.

#### 8.3.7.1 Unique 64-Bit Device Address and ID

The device has a hard-coded, 64-bit address which is factory programmed and cannot be altered by the customer application. The unique 64-bit device address is used for device addressing in the end application and for NIST traceability. 8-3 shows the format of the 64-bit address. When the host accesses the device or when the device sends its address, the 64-bit unique address is sent least significant bit first. The unique 64-bit address consists of 3 fields. The lower 8 bits consists of the device family code, followed by a 48-bit unique number and 8-bit CRC checksum on the 56 bits preceding it.

The device family code for TMP1827 shall read as 27h.

图 8-3. 64-Bit Device Address

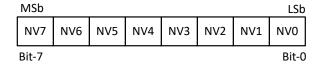

### 8.3.8 Flexible Device Address

Depending on the user application case, the TMP1827 provides for some user and application configurable address modes, called flexible address mode. These modes exist along side the standard device address, and is extremely useful for applications that require a combination of faster access and device position identification.

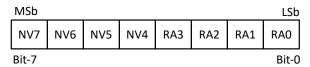

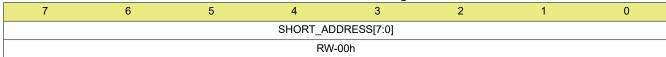

When the flexible device address is used, the short address register is updated. The short address register shall be updated by the host write when the FLEX\_ADDR\_MODE bits are '00b'. When these bits have a value other than '00b', the resulting decode of the resistor connected on ADDR pin or IOs shall be overlaid on the short

address register. This is helpful as the same set of 16 resistors or 16 IO combinations can be used to extend the number of unique flexible address up to 256.

The FLEX\_ADDR\_MODE is not backed in the configuration EEPROM. Hence after decoding, the host must ensure that copy to configuration EEPROM is performed to make the short address values permanent, without having to decode at every power up.

#### 8.3.8.1 Non-Volatile Short Address

图 8-4. Non-Volatile Short Address

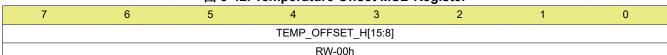

#### 8.3.8.2 IO Hardware Address

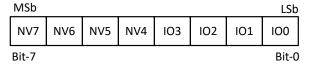

$\boxtimes$  8-5 shows the 8-bit IO hardware address mode of the device. This feature is available on packages which have general-purpose pins (IO0-IO3) available. The 8-bit value consists of the lower 4 bits as read values of the pins (IO3 to IO0) that is overlaid on the contents of the short address register to form a 8-bit address. The application may connect the general-purpose pins to either  $V_{DD}/SDQ$  for logic '1' or GND for logic '0'.

After power up, the host must set the bits FLEX\_ADDR\_MODE[1:0] as '01b' in the device configuration-2 register for the device to latch the state of the general-purpose pins.

图 8-5. IO Hardware Address

备注

If any of the IO0 to IO3 pins are used in output mode, then the respective value shall be latched as '0'.

#### 8.3.8.3 Resistor Address

The resistor address modes uses a 1% tolerance resistor connected between the ADDR pin and ground.

8-6 shows the 8-bit address with the lower 4 bits decoded from the resistor connected, which is overlaid on the contents of the short address register.

图 8-6. Resistor Address

After power up, the host controller sets the bits FLEX\_ADDR\_MODE[1:0] as '10b' in the device configuration-2 register which enables the device to sample the pin and identify the resistor connected. After writing the device configuration-2 register, the host must idle the bus for  $t_{RESDET}$ , for the device to decode the resistor address.  $\gtrsim$  8-3 shows the set value of the device address based on the decoded resistor value. If the ADDR pin connected to GND or lower than 6.49 k $\Omega$ , then the address decoder shall always decode as '0000b'. Similarly, if the ADDR pin is connected to a resistor higher than 54.9 k $\Omega$ , the address decoder shall always decode as '1111b'.

The host controller must ensure that CONV\_MODE\_SEL[2:0] is set as '000b' when decoding the resistor address.

表 8-3. Resistor Address Decode

| RESISTOR VALUE (k Ω) | ADDRESS DECODE |

|----------------------|----------------|

| < 6.49               | 0h             |

| 7.87                 | 1h             |

| 9.31                 | 2h             |

| 11.0                 | 3h             |

| 13.3                 | 4h             |

| 15.4                 | 5h             |

| 17.8                 | 6h             |

| 20.5                 | 7h             |

| 23.7                 | 8h             |

| 26.7                 | 9h             |

| 30.1                 | Ah             |

| 33.2                 | Bh             |

| 37.4                 | Ch             |

| 44.2                 | Dh             |

| 47.5                 | Eh             |

| > 54.9 or floating   | Fh             |

This mode is useful when the application requires placing the TMP1827 on multiple printed circuit boards (PCBs). The Bill of Materials (BOM) component can be changed easily instead of having multiple PCBs fabricated for individual pin connections, thereby reducing the cost of the system.

#### 备注

The ADDR pin if unused, must be connected to GND. The  $C_{LOAD}$  for ADDR pin is due to parasitic capacitance depending on the board layout. There is no requirement to place an external capacitor on the ADDR pin.

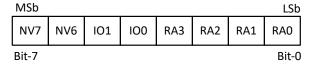

#### 8.3.8.4 Combined IO and Resistor Address

In the combined IO and resistor address mode, the IO0 and IO1 pin is used along with the resistor connected between ADDR pin and ground. 🛭 8-7 shows the 8-bit address with the lower 4 bits decoded from the resistor connected, followed by 2 bits decoded from the IO0 and IO1 pins which may be connected to either VDD/SDQ for logic '1' or GND for logic '0', which is overlaid on the contents of the short address register.

After power up, the host sets the bits FLEX\_ADDR\_MODE[1:0] as '11b' in the device configuration-2 register which enables the device to sample the ADDR pin to identify the resistor connected, followed by sampling of the IOO and IO1 to configure the short address. If the bit field value has already been updated in the non-volatile storage, then the device shall automatically latch the pins, run the resistor decoder, and update the value in the short address register on power up.

The host controller must ensure that CONV\_MODE\_SEL[2:0] is set as '000b' when decoding the resistor address.

图 8-7. Combined IO and Resistor Address

Submit Document Feedback

This mode is useful when the application requires placing up to 64 devices on a single PCB, as it allows for easy expansion using a combined approach of IO and resistor decoding while enabling IO2 and IO3 to function as general-purpose input and output pins. This mode may also be used for position identification as no two devices may have the same short address.

#### 备注

If the IO0 or IO1 pins are used in output mode, then the respective value shall be latched as '0'.

#### 8.3.9 CRC Generation

The TMP1827 implements a cyclic redundancy check (CRC) mechanism for data integrity check and communication robustness.  $\frac{1}{8}$  8-4 lists the properties of a 8-bit CRC.

| CRC-8 Rule            | Attributes                                                  |

|-----------------------|-------------------------------------------------------------|

| CRC width             | 8 bits                                                      |

| CRC polynomial        | x <sup>8</sup> + x <sup>5</sup> + x <sup>4</sup> + 1 (0x31) |

| Initial seed value    | 00h                                                         |

| Input data reflected  | Yes                                                         |

| Output data reflected | Yes                                                         |

| XOR value             | 00h                                                         |

When a new transaction is done, the shift register is initialized with the seed value of 00h and the data is shifted in LSB first. The CRC result is always part of the 64-bit unique address and is computed on the 56-bits that precede it. Additionally, when the host writes to the scratchpad-1 for the registers and scratchpad-2 for the memory, the device sends the CRC computed on the data bytes to provide a data integrity check for the host on the transaction. When the host reads the scratchpad-1 for reading the temperature register, the device shall append the CRC after the 8 bytes of scratchpad are sent.

The host must recalculate the CRC and compare it against the received CRC from the device. This is done by shifting the read data from the device along with CRC bits. If there is no bus error, then the shift register at the end of the bit shift will result in 00h. When writing the data to the device, the host must check the CRC received by processing the write data to ensure that there were no transmission errors and take appropriate corrective action before performing the next function.

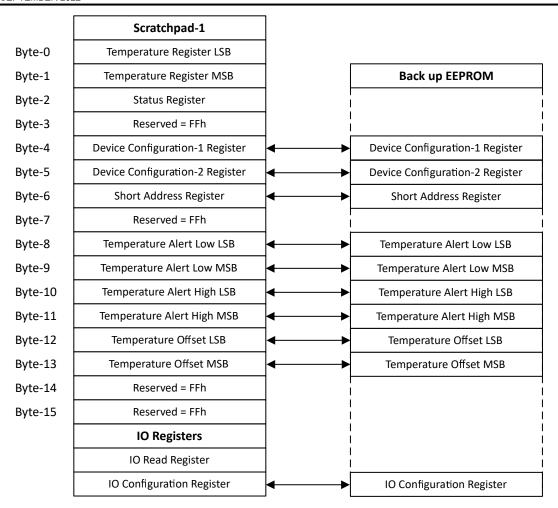

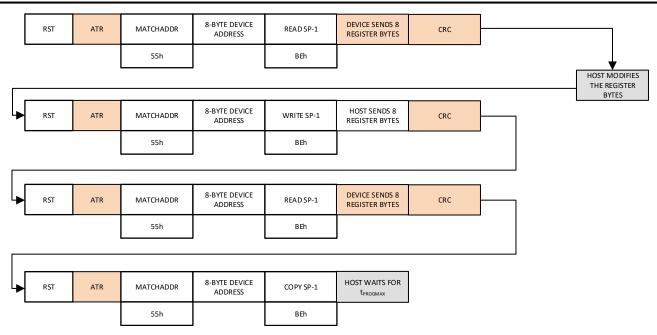

#### 8.3.10 Functional Register Map

The scratchpad-1 region and the IO register region together are referred to as the functional register map (see 8-8). The scratchpad-1 region is 16 bytes deep, and has temperature result, device status, device configuration, short address, temperature alert limit and temperature offset registers. The IO register region has the IO read and IO configuration registers. Some of the registers can be committed to the configuration EEPROM to ensure that the device settings are restored on power up without the host rewriting the configuration.

图 8-8. Functional Register Map (Scratchpad-1)

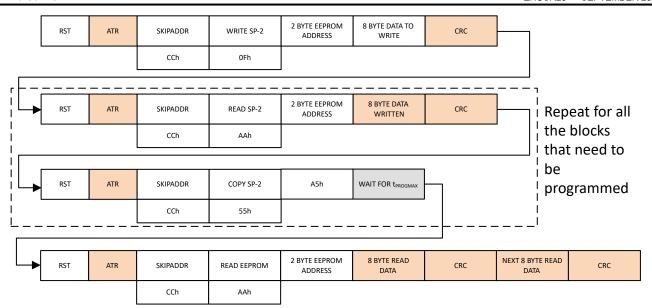

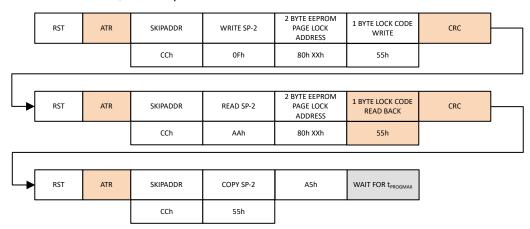

#### 8.3.11 User Memory Map

The EEPROM memory is organized as 8 pages of 4 blocks each. 8 8-9 shows that each block is 8 bytes or 64 bits. This results in a total user memory of 2048 bits. All memory access to the device shall be increments of a block size of 8 bytes. Access to the memory for programming is done through the scratchpad-2 register. The host writes to the scratchpad-2 register, which allows the device to perform a read before committing the content to the memory.

Product Folder Links: TMP1827

Submit Document Feedback

| 1            | 00FFh          |            | Block 3 | 00F8h – 00FFh |

|--------------|----------------|------------|---------|---------------|

|              |                | Page 7     | Block 2 | 00F0h – 00F7h |

|              |                | rage /     | Block 1 | 00E8h – 00EFh |

|              | 00E0h          |            | Block 0 | 00E0h – 00E7h |

|              | 00DFh          |            | Block 3 | 00D8h – 00DFh |

|              |                | Page 6     | Block 2 | 00D0h – 00D7h |

|              |                | rage 0     | Block 1 | 00C8h – 00CFh |

|              | 00C0h          |            | Block 0 | 00C0h – 00C7h |

|              | 00BFh          |            | Block 3 | 00B8h – 00CFh |

|              |                | Dana F     | Block 2 | 00B0h – 00B7h |

|              |                | Page 5     | Block 1 | 00A8h – 00AFh |

|              | 00A0h<br>009Fh |            | Block 0 | 00A0h – 00A7h |

|              |                |            | Block 3 | 0098h – 009Fh |

|              |                | Dage 4     | Block 2 | 0090h – 0097h |

| S            |                | Page 4     | Block 1 | 0088h – 008Fh |

| yte          | 0080h          |            | Block 0 | 0080h – 0087h |

| 256 bytes    | 007Fh          |            | Block 3 | 0078h – 007Fh |

| 2            |                | Page 3     | Block 2 | 0070h – 0077h |

|              |                | rage 5     | Block 1 | 0068h – 006Fh |

|              | 0060h          |            | Block 0 | 0060h – 0067h |

|              | 005Fh          |            | Block 3 | 0058h – 005Fh |

|              |                | Daga 2     | Block 2 | 0050h – 0057h |

|              |                | Page 2     | Block 1 | 0048h – 004Fh |

|              | 0040h          |            | Block 0 | 0040h – 0047h |

|              | 003Fh          |            | Block 3 | 0038h – 003Fh |

|              |                | Dago 1     | Block 2 | 0030h – 0037h |

|              |                | Page 1     | Block 1 | 0028h – 002Fh |

|              | 0020h          |            | Block 0 | 0020h – 0027h |

|              | 001Fh          | <u></u>    | Block 3 | 0018h – 001Fh |

|              |                | -32 bytes- | Block 2 | 0010h – 0017h |

|              |                | γ Page 0   | Block 1 | 0008h – 000Fh |

| $\downarrow$ | 0000h          | <b>Ŭ</b>   | Block 0 | 0000h – 0007h |

|              |                |            |         |               |

图 8-9. Address to EEPROM Page and Block Map

#### 备注

The device shall return "1" for any device read without a CRC if the address is outside the user memory map.

#### 8.3.12 SHA-256-HMAC Authentication Block

The authentication block on the TMP1827 device uses a keyed-hash message authentication code (HMAC) which is FIPS PUB-198-1 compliant SHA-256 hash implementation. The SHA-256 implementation itself is FIPS PUB-180-4 compliant. The HMAC engine does not encrypt the data, but generates a 256-bit hash based on the user programmed keys.

For details on SHA-256-HMAC authentication block, refer to the TMP1827 Security Programming Guide.

#### 8.3.13 Bit Communication

The single-wire interface communication does not have a reference clock, therefore all communication is performed asynchronously with fixed time slot (t<sub>SI OT</sub>) and variable pulse width to indicate logic '0' and '1'. In idle state, the external pullup resistor holds the line high. All bit communication, whether it is a write or a read, are initiated by the host by driving the data line low to generate a falling edge and the bit value is decoded as the time for which the data line is held low or high after the falling edge.

Even though the communication is one bit at a time, the data exchanged between the host and device is performed at byte boundary. Every byte is sent least significant bit first. The device behavior is not ensured when incomplete bytes are sent.

#### 8.3.13.1 Host Write, Device Read

A host write is the means by which the host sends the command, function, and data to the devices. A host write starts by the host driving the data line low as shown in \alpha 8-10. If the host intends to transmit a logic '1', the line is released after twR1L time. If the host intends to transmit a logic '0', the line is released after twR0L. After releasing the data, the pullup resistor causes the line to become high till the beginning of the next time slot. The device samples the line after  $t_{RDV}$  has elapsed from the falling edge, for a time frame indicated by  $t_{DSW}$ . The host must factor the rise time due to the pullup resistor and bus capacitance to determine the release of the data line before the line is sampled by the device and the host drives the next write bit time slot.

图 8-10. Host Write, Device Read

#### 8.3.13.2 Host Read, Device Write

A host read is the means by which the hosts gets the data from the device or the CRC for data integrity check. A host read starts by the host driving the data line low as shown in \( \bigsig 8-11. \) When the device detects the falling edge, the device can drive the line low before the time t<sub>RL</sub>. The host can release the bus from the side after the time t<sub>RL(MIN)</sub> elapses. If the device intends to transmit a logic '1', then the bus is released before t<sub>RL(MAX)</sub> elapses. If the device intends to transmit a logic '0', then the bus is released after t<sub>SLOT(MIN)</sub>. The host must sample the line after the time t<sub>RWAIT</sub>, for a time frame indicated by t<sub>MSW</sub>. The host must factor the rise time due to the pullup resistor and bus capacitance to determine the sampling window for the host to sample the bit level sent by the device or to drive the next read bit time slot.

图 8-11. Host Read, Device Write

# 8.3.14 Bus Speed

The device supports both standard speed (8.33 kbps) and overdrive speed (90 kbps) data rates. All devices are factory programmed to start in overdrive speed, to enable higher data throughput. If the host requires the device to operate at standard speed, then it can easily switch the device by issuing a standard speed bus reset. The seamless switch over allows host to leverage better data rates on new designs, while maintaining backward compatibility for older design.

Additionally, the device also provides the flexibility to switch from standard to overdrive speed mode using address phase commands of OVD SKIPADDR and OVD MATCHADDR.

- When host issues OVD SKIPADDR, then all devices on the bus switch from standard speed to overdrive speed.

- When host issues OVD MATCHADDR, then the device whose 64-bit device address matches the address that host sends, will switch from standard to overdrive speed.

#### 8.3.15 NIST 可追溯性

使用由符合 ISO/IEC 17025 政策和程序的经认证实验室校准的设备对温度测试精度进行了验证。每款器件都经过测试和微调,确保满足其各自的数据表规格限值。

#### 8.4 Device Functional Modes

The TMP1827 device features flexible temperature conversion modes along with robust user EEPROM architecture, which is described in the sections below.

#### 8.4.1 Conversion Modes

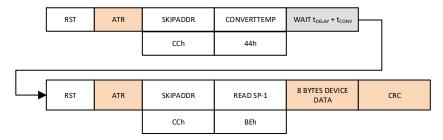

The TMP1827 supports both one-shot and continuous conversion modes. There are different methods for one-shot conversion modes, that may be used based on single device or multiple device bus network. The continuous conversion mode is only supported in  $V_{DD}$  powered mode. Each of the conversion modes are with single temperature sample, but the host can enable 8 samples averages in the device for improved accuracy.

#### 8.4.1.1 Basic One-Shot Conversion Mode

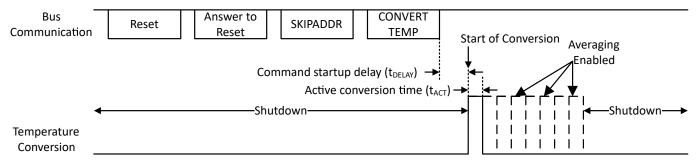

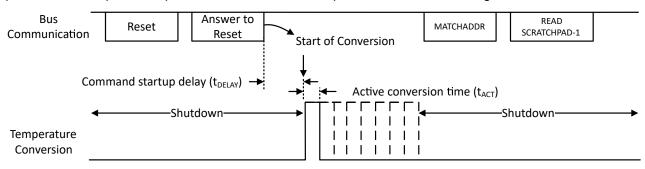

The basic one-shot conversion mode is the default conversion mode. The device goes through a bus reset, address and function phase to initiate the temperature conversion. During the communication, the device is in shutdown mode. When the conversion request is registered by the device, the device starts active conversion and then goes back to low power shutdown mode as shown in 88 8-12. If the device is in continuous conversion mode, then the one-shot conversion mode request is ignored.

图 8-12. One-Shot Conversion Mode

As shown in 88-13, there is no change in how one-shot conversion is performed when there are multiple devices on the bus. However, as there are multiple devices, the combined current drain in bus powered mode of operation may cause the bus voltage to drop. In such use cases, it is required that the host implement a low impedance current path using a FET/transistor switch. This path is switched on so as to meet the current requirement of the bus during an active conversion and after the active conversion duration is complete, it is switched off for bus communication.

图 8-13. Multiple Device One-Shot Conversion Mode

Product Folder Links: TMP1827

ubmit Document Feedback

#### 8.4.1.2 Auto Conversion Mode

The auto conversion mode is a programmable feature in bus powered mode that can be enabled by setting the CONV\_MODE\_SEL as '10b' in the device configuration-1 register. As shown in 🗵 8-14, the host can skip the issue of the temperature conversion request and directly read the temperature data from the device when the auto conversion mode is enabled. This enables the application to speed up the temperature conversion and read, because the request command is no longer required. As in the case for multiple device bus, a low impedance current path is required to meet the current requirement of the bus during the active conversions.

图 8-14. Auto Conversion Mode

#### 8.4.1.3 Stacked Conversion Mode

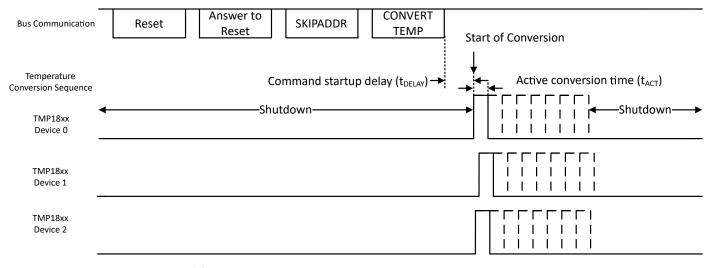

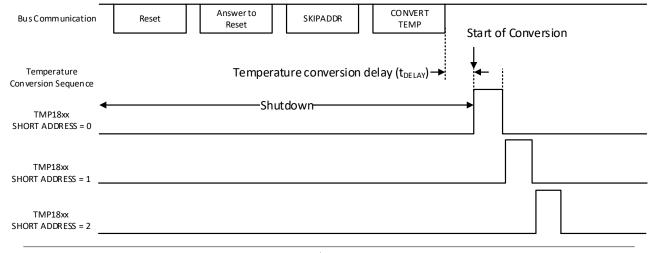

The stacked conversion mode is a programmable feature in bus powered mode that can be enabled by setting CONV\_MODE\_SEL as '01b' in the device configuration-1 register. As shown in 🗵 8-15, the devices can use the address programmed in the short address register to delay the temperature conversion for the devices when the stacked conversion mode is enabled. No more than two devices are actively converting at any given time, therefore the current drain in bus powered configuration is limited. This allows the application to avoid simultaneous temperature conversion by multiple parts and reducing the user system maximal supply current.

备注

The host controller must program all the device with the same setting for CONV\_TIME\_SEL and AVG\_SEL to ensure that no more than two devices are actively converting to use the feature as it is intended.

图 8-15. Stacked Conversion Mode

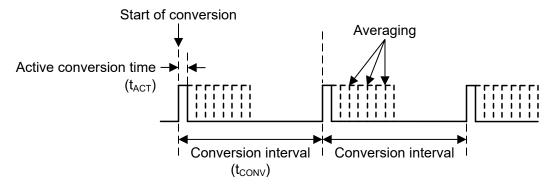

#### 8.4.1.4 Continuous Conversion Mode

The continuous conversion mode is applicable only in  $V_{DD}$  powered mode of operation for the device. This mode can be enabled by writing a value other than '000b' to CONV\_MODE\_SEL bits in the device configuration-1

register. As shown in 88-16, the device can perform periodic conversions at the interval programmed by the host and updates the temperature result register when continuous conversion mode is enabled. The device also performs the alert threshold check and sets the flags and alert pin, if configured accordingly. When in continuous conversion mode, the CONVERTTEMP function has no effect on the temperature conversion request. The application can at any time change the rate of conversion or put the device back into one-shot conversion mode, and this takes effect only after the current conversion is complete.

图 8-16. Continuous Conversion Mode

If due to any reason, the  $V_{DD}$  supply fails without the device going through a brown out, causing the device to move to bus powered mode of operation, the conversion mode automatically reverts to the setting in the configuration EEPROM.

#### 8.4.2 Alert Function

As described earlier, the built-in alert function can be used by the host to check if the temperature has crossed a certain threshold. The alert status bits are available in both bus powered and  $V_{DD}$  powered mode. The alert pin is available only in  $V_{DD}$  powered mode.

If the device is in  $V_{DD}$  powered mode and IO2/ALERT is configured to function as an IO2/ALERT pin, then the pin shall be driven active low when the threshold crossing occurs. The pin is open-drain, and therefore requires a pullup resistor. The IO2/ALERT pin deassertion is based on the setting of the ALERT\_MODE setting in the device configuration-1 register.

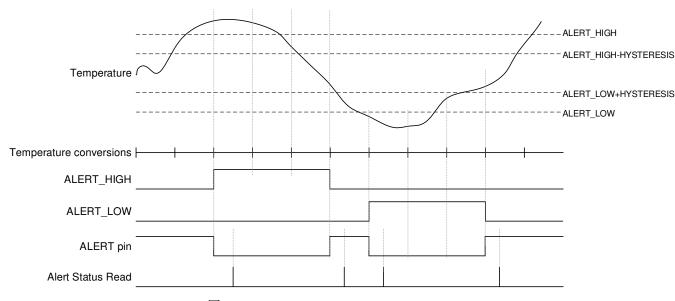

#### 8.4.2.1 Alert Mode

The device operates in alert mode, when the ALERT\_MODE is set as '0b'. In the alert mode of operation, the alert status flag and IO2/ALERT pin are asserted when the last temperature conversion is either higher than the temperature alert high limit or when it is lower than the temperature alert low limit register.

The alert status flag and IO2/ALERT pin are deasserted only when the host reads the status register or performs a successful ALERTSEARCH command as shown in § 8-17.

图 8-17. Alert Mode Timing Diagram

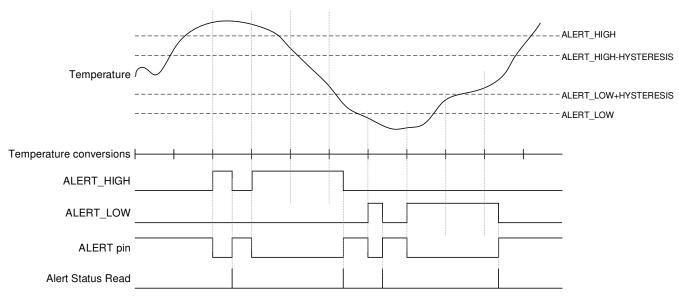

# 8.4.2.2 Comparator Mode

The device operates in comparator mode, when the ALERT\_MODE is set as '1b'. In the alert mode of operation, the alert status flag and IO2/ALERT pin are asserted when the last temperature conversion is either higher than the temperature alert high limit or when it is lower than the temperature alert low limit register.

The alert status flag and IO2/ALERT pin are deasserted only when the result of the last temperature conversion is less than the temperature alert high limit minus the hysteresis or above the temperature low limit plus the hysteresis as shown in 🖺 8-18. The hysteresis is selectable using the HYSTERESIS bit field in the device configuration-2 register.

图 8-18. Comparator Mode Timing Diagram

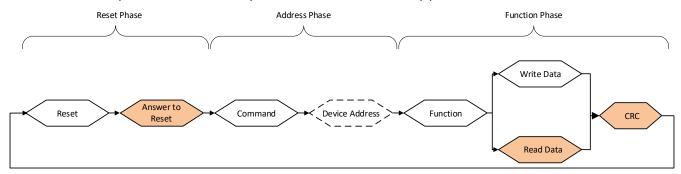

# 8.4.3 Single-Wire Interface Communication

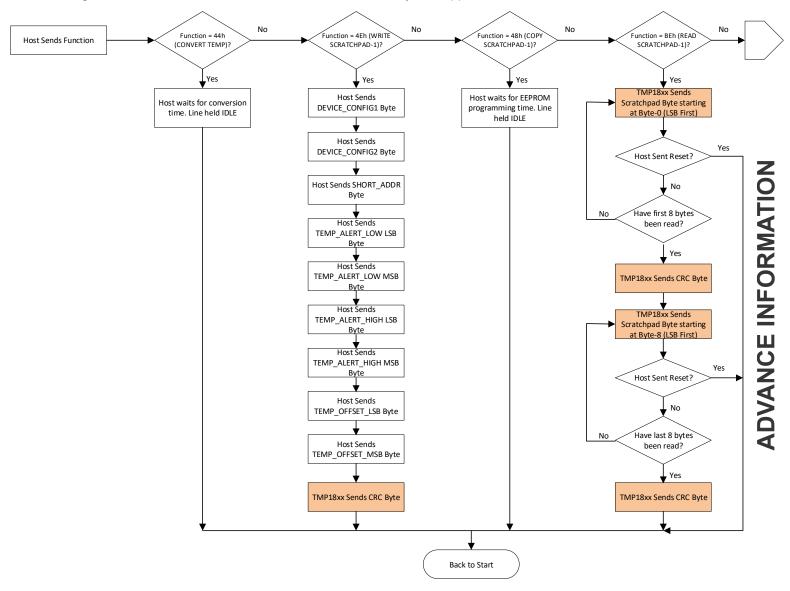

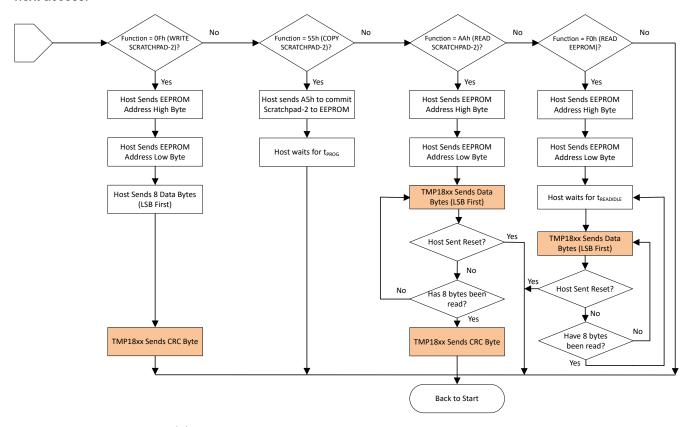

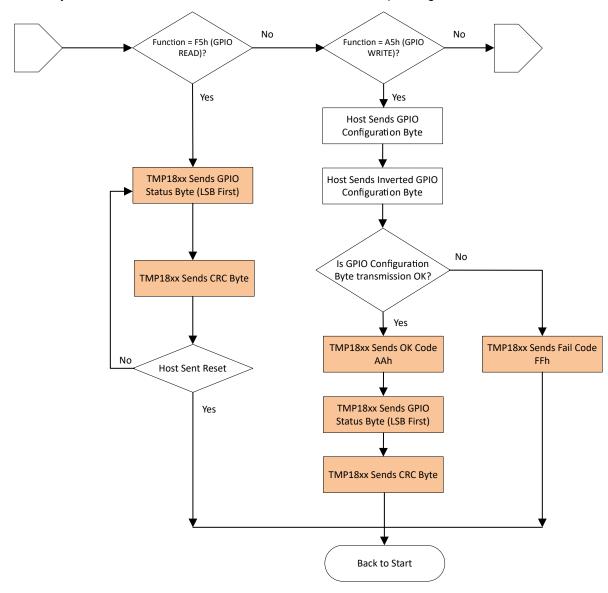

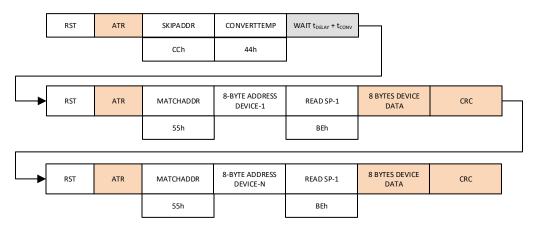

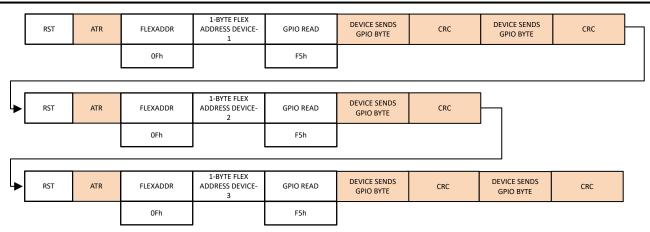

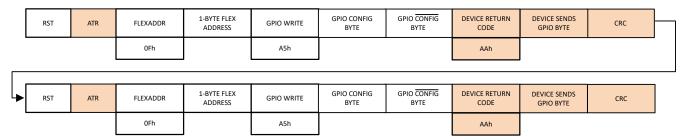

To leverage the features effectively, the device access consists of 3 distinct phases. As shown in 🗵 8-19, any bus communication starts with a bus reset condition to which every device on the bus must respond. This is followed by a highly configurable address phase, where the host selects the device it wants to access. Finally, there is a function phase where the host provides the selected device(s) the action it wants to take.

图 8-19. Single-Wire Bus Communication

In a single-wire bus, all write and reads are initiated by the host except for the answer to reset which is initiated by the devices on the bus.

#### 8.4.3.1 Bus Reset Phase

The bus reset phase is the beginning of the communication. The phase is initiated by the host by holding the single-wire data line low for a period t<sub>RSTL</sub>. All devices on the bus, irrespective of their current state shall respond to the bus reset, by reinitializing their internal state and responding to the host initiated bus reset. The devices respond after a minimum of  $t_{PDH}$ , by holding the single-wire low for a time period of  $t_{RSTH}$  as shown in  $\boxtimes$  7-1.

All devices are configured with the OD\_EN bit set as '1' in the device configuration-2 register. If the host sends a bus reset pulse of 48 µs to 80 µs, then only devices operating in overdrive speed shall respond to the bus reset pulse, while devices operating in standard mode shall continue to wait for a standard mode bus reset.

If the host sends a bus reset pulse of minimum t<sub>RSTL</sub> for standard mode, the device shall reset the OD\_EN bit to '0' and respond to the bus reset in standard mode. If the bus consists of mixed standard and overdrive speed devices, then sending a bus reset pulse in standard mode shall reset all devices to standard mode speed of operation.

It is illegal for the host to send the bus reset for a particular speed of operation and then communicate at the other speed mode. Also, if a bus reset pulse is sent which is greater than 80 µs (but less than 480 µs), then the device shall be reset, though the device operation is not ensured.

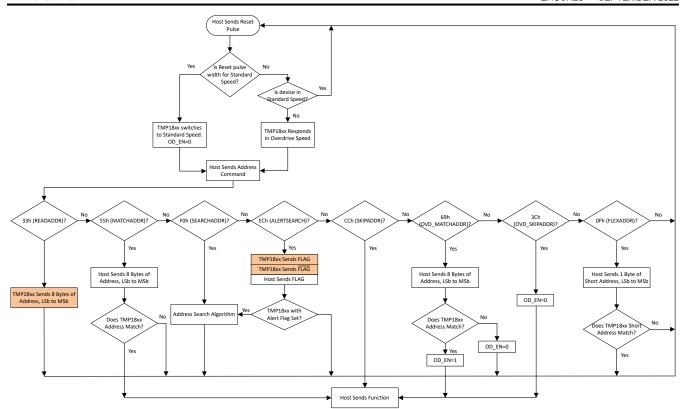

#### 8.4.3.2 Address Phase

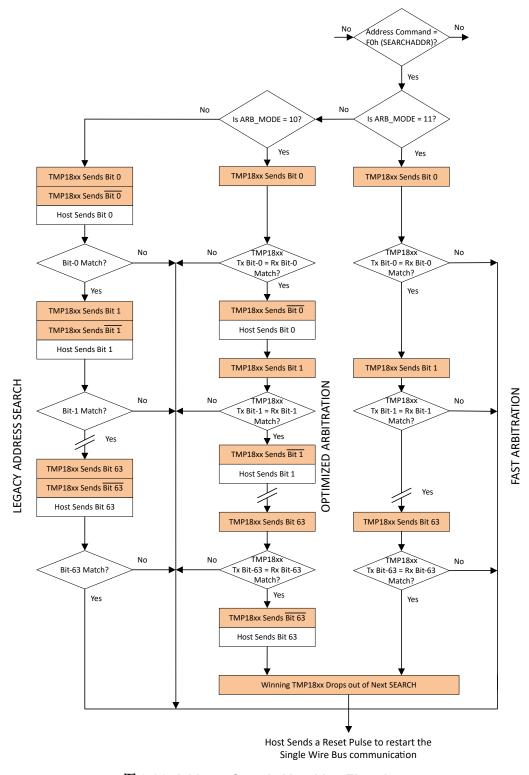

🛚 8-20 shows the address phase that follows the bus reset phase. During this phase, the host presents 8-bit commands which may be followed by either host sending a 64-bit device address, a 8-bit flexible address, or skipping the address. Some of the commands are used to discover the device address, while others are used to select the device.

图 8-20. Address Phase Flowchart

### 8.4.3.2.1 READADDR (33h)

The command can be used by the host to read the 64-bit address of the device. This command must only be used when there is one device on the bus, as this command will cause a collision if multiple devices are present on the bus.

# 8.4.3.2.2 MATCHADDR (55h)