TUSB2E11

ZHCSQH7B - NOVEMBER 2021 - REVISED AUGUST 2023

# TUSB2E11 USB 2.0-eUSB2 中继器

### 1 特性

- 兼容 USB 2.0 和 eUSB2 ( 1.2 版 )

- 低速、全速、高速信令

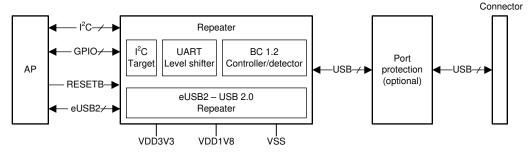

- 20ps 卓越高速总抖动

- 寄存器访问协议接收器功能

- 支持主机和器件模式(双重角色器件)

- 自动检测 I2C 或自举引脚选项

- 用于 USB 2.0 高速通道补偿设置的三个自举引

- I<sup>2</sup>C 器件接口支持更多配置

- 器件变体

- eUSB2 1.0V 或 1.2V 信令接口

- 适用于不同产品外形尺寸的 eUSB2 布线损耗补 偿水平

- 1.2V 或 1.8V I<sup>2</sup>C 接口

- 支持可选电池充电和检测

- BC 1.2 CDP 或 DCP 分频器模式广播

- 数据感知 USB Type-C™ 兼容 BC 1.2 SDP、 CDP 和 DCP 分频器模式检测

- 充电器广播或检测之间的双重角色自动切换

- 支持 CTA-936 USB Carkit UART

- 支持自动恢复 ECR 以及 L2 中断恢复模式

- 可选 GPIO:中断 GPIO2、调试、I<sup>2</sup>C ↔ GPIO0/1

- I2C 可访问调试功能适用于制造测试

#### 2 应用

- 笔记本电脑和台式机

- 手机

- 平板电脑

- 可穿戴设备

- 便携式电子产品

# 3 说明

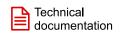

TUSB2E11 是一款支持器件和主机模式的 USB 兼容 eUSB2 至 USB 2.0 中继器。

器件支持 USB 低速 (LS)、全速 (FS) 和高速 (HS) 信

该器件采用多项专利设计,可提供强大的互操作性、性 能和电源。

对于没有 I<sup>2</sup>C 接口的系统,该器件提供 8 个单独的设 置,带有三个适用于高达  $20\Omega$  的 USB 2.0 通道等效串 联电阻 (ESR) 的自举引脚。器件变体可用于高达 10 英 寸的不同级别的 eUSB2 布线长度补偿。

I<sup>2</sup>C 接口可提高灵活性,支持微调器件的 RX 均衡性和 TX 振幅、压摆率和预加重,以便通过电气合规性测试 并补偿通道损耗。

可通过 3 个 GPIO 引脚提供各种调试选项,这些引脚 可配置来监控各种 USB 总线状态或中断,以及提供 SoC 调试功能的 CTA-936 UART 模式。GPIO0 和 GPIO1 可用作通用  $I^2C$  至 GPIO 桥接器件。

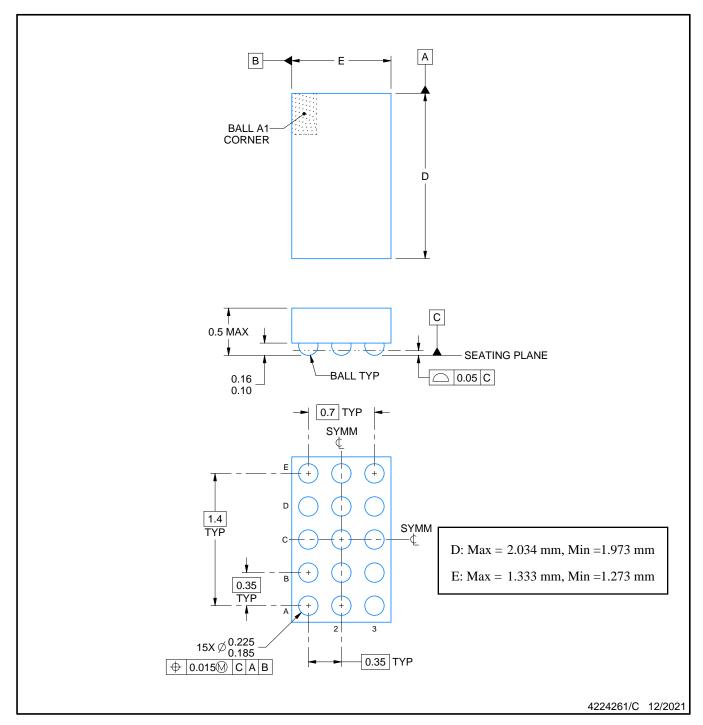

#### 封装信息

| 器件型号 <sup>(1)</sup> | 封装 <sup>(2)</sup>     | 封装尺寸 <sup>(3)</sup> |

|---------------------|-----------------------|---------------------|

| TUSB2E11            | YCG ( DSBGA ,<br>15 ) | 1.75mm × 1.05mm     |

- (1) 请参阅器件比较

- 如需了解所有可用封装,请参阅数据表末尾的可订购产品附 (2)

- 封装尺寸(长×宽)为标称值,并包括引脚(如适用)。

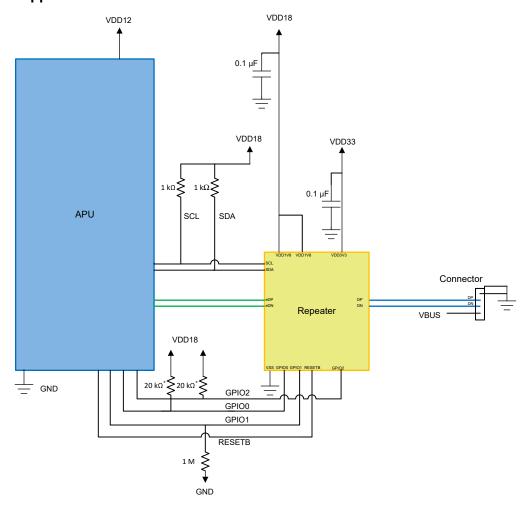

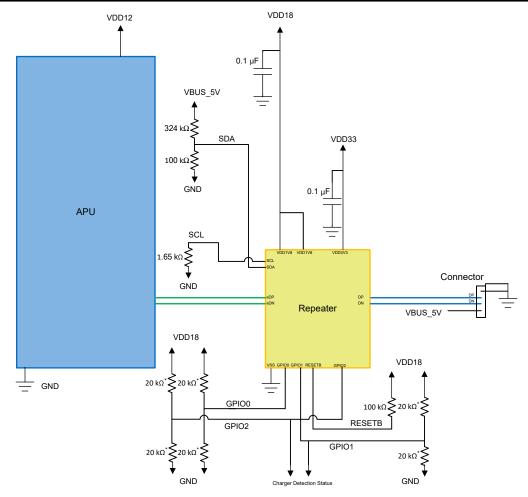

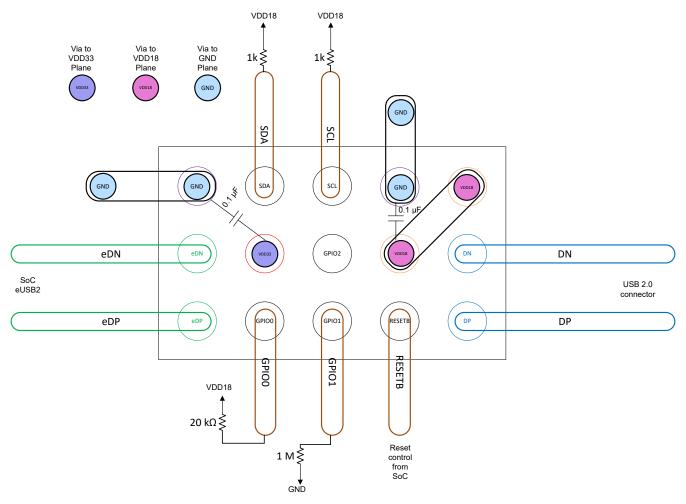

简化版应用

# **Table of Contents**

| 1 特性                                 | 1  | 9.4 Device Functional Modes             | 24               |

|--------------------------------------|----|-----------------------------------------|------------------|

| 2 应用                                 |    | 9.5 Manufacturing Test Modes            |                  |

| - ፫/,1<br>3 说明                       |    | 9.6 I <sup>2</sup> C Target Interface   |                  |

| 4 Revision History                   |    | 10 Register Access Protocol (RAP)       |                  |

| 5 Device Version Comparison          |    | 11 Register Map                         |                  |

| 5.1 Device Variants                  |    | 11.1 TUSB2E11 Registers                 |                  |

| 6 Pin Configuration and Functions    |    | 12 Application and Implementation       | 45               |

| 7 Specifications                     |    | 12.1 Application Information            | 45               |

| 7.1 Absolute Maximum Ratings         |    | 12.2 Typical Application                |                  |

| 7.2 ESD Ratings                      |    | 12.3 Power Supply Recommendations       | 48               |

| 7.3 Recommended Operating Conditions |    | 12.4 Layout                             |                  |

| 7.4 Thermal Information              |    | 13 Device and Documentation Support     | <mark>5</mark> 1 |

| 7.5 Electrical Characteristics       |    | 13.1 Device Support                     | <mark>5</mark> 1 |

| 7.6 Switching Characteristics        |    | 13.2 Documentation Support              | <mark>5</mark> 1 |

| 7.7 Timing Requirements              |    | 13.3 接收文档更新通知                           | <mark>5</mark> 1 |

| 7.8 Typical Characteristics          |    | 13.4 支持资源                               |                  |

| 8 Parameter Measurement Information  |    | 13.5 Trademarks                         |                  |

| 9 Detailed Description               | 23 | 13.6 静电放电警告                             | <mark>5</mark> 1 |

| 9.1 Overview                         |    | 13.7 术语表                                |                  |

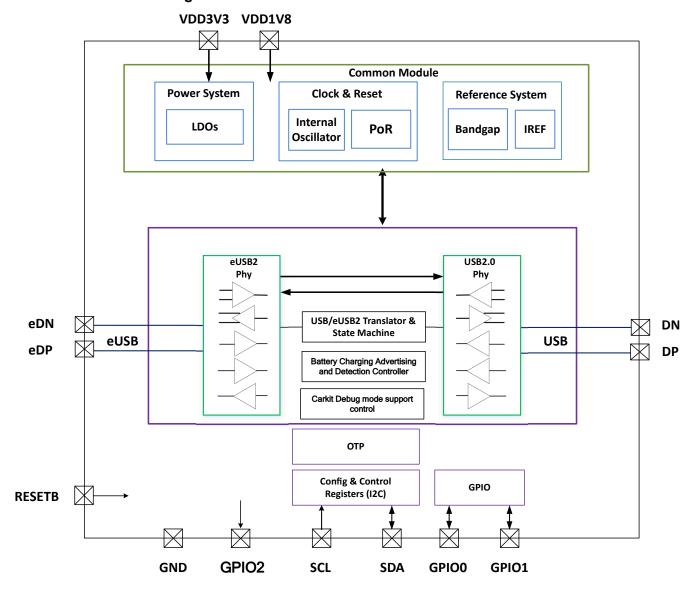

| 9.2 Functional Block Diagram         |    | 14 Mechanical, Packaging, and Orderable |                  |

| 9.3 Feature Description              |    | Information                             | <u>5</u> 1       |

4 Revision History 注:以前版本的页码可能与当前版本的页码不同

| Changes from Revision A (June 2022) to Revision B (August 2023)        | Page |

|------------------------------------------------------------------------|------|

| • 更新了封装信息表以包含封装引线尺寸                                                    | 1    |

| Updated Recommended Operating Conditions to clarify the ROC for RESETB | 9    |

| Updated register F5h to indicate OPN variants                          | 33   |

| Changes from Revision * (November 2021) to Revision A (June 2022)      | Page |

| • 首次公开发布数据表                                                            | 1    |

Product Folder Links: TUSB2E11

# **5 Device Version Comparison**

#### 表 5-1. Device Register Comparison Table

|         | Register Address | B0 default | B1 default |

|---------|------------------|------------|------------|

| 表 11-5  | 0x70h            | 0x73h      | 0x7Ch      |

| 表 11-6  | 0x71h            | 0x38h      | 0x3Ch      |

| 表 11-7  | 0x72h            | 0x90h      | 0x92h      |

| 表 11-8  | 0x73h            | 0x04h      | 0x83h      |

| 表 11-9  | 0x77h            | 0x00h      | 0x00h      |

| 表 11-10 | 0x78h            | 0x0Bh      | 0x0Bh      |

| 表 11-11 | 0x79h            | 0x40h      | 0x60h      |

| 表 11-12 | 0x50h            | 0x02h      | 0x02h      |

| 表 11-13 | 0xB0h            | 0x02h      | 0x03h      |

| 表 11-14 | 0xB2h            | 0x00h      | 0x00h      |

| 表 11-15 | 0xB3h            | 0x00h      | 0x00h      |

| 表 11-16 | 0xB4h            | 0x00h      | 0x00h      |

| 表 11-17 | 0xB6h            | 0xC0h      | 0xC0h      |

| 表 11-21 | 0x60h            | 0x00h      | 0x00h      |

| 表 11-22 | 0xF5h            | 0x32h      | 0x32h      |

#### 表 5-2. Device Feature Comparison Table

| Features                      | В0            | B1                                                  |

|-------------------------------|---------------|-----------------------------------------------------|

| Low Power Mode (RESETB = low) | not supported | supported (9 μW)                                    |

| Auto-resume ECR               |               | supported (enabled by default) [see register 0x78h] |

| L2 State Interrupt Resume     | supported     | supported                                           |

#### **5.1 Device Variants**

The following table describes the key differences between TUSB2E11x device variants.

#### 表 5-3. Device Variant Information

| Orderable Device | Package Type | Package Drawing | Pins | Version | I/O Voltage <sup>(1)</sup> | Device Marking |

|------------------|--------------|-----------------|------|---------|----------------------------|----------------|

| TUSB2E111YCGR    | WCSP         | YCG             | 15   | B1      | 1.8V                       | T2E111A        |

| TUSB2E112YCGR    | WCSP         | YCG             | 15   | B1      | 1.2V                       | T2E112         |

<sup>(1)</sup> I/O Voltage: I2C Bus voltage and GPIO voltage

For more information and availability of device variants such as eUSB2 1.0 signaling interface, 1.2 V I<sup>2</sup>C interface, and 1.2 V GPIO interface please contact support.

# **6 Pin Configuration and Functions**

图 6-1. TUSB2E11 YCG Package, 15-Pin DSBGA (Top View)

表 6-1. Pin Functions

| PIN    |        | TYPE <sup>(2)</sup> | REST  | ASSOCIATED ESD | DESCRIPTION                                                                                                                                                                                                                                                                  |  |  |

|--------|--------|---------------------|-------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NO.    |                     | STATE | SUPPLY         |                                                                                                                                                                                                                                                                              |  |  |

| VDD3V3 | B2     | PWR                 | N/A   | N/A            | 3.3 V Supply Voltage                                                                                                                                                                                                                                                         |  |  |

| VDD1V8 | D2, E3 | PWR                 | N/A   | N/A            | 1.8 V Supply Voltage                                                                                                                                                                                                                                                         |  |  |

| VSS    | A3, D3 | GND                 | N/A   | N/A            | GND                                                                                                                                                                                                                                                                          |  |  |

| RESETB | D1     | I                   | N/A   | VDD1V8         | <ul> <li>Active Low Reset</li> <li>Upon de-assertion of RESETB, repeater will be enabled and be in eUSB2 default mode awaiting configuration from eDSPr or eUSPr.</li> <li>If RESETB is not actively controlled, a pull-up resistor 100 kΩ to VDD1V8 is required.</li> </ul> |  |  |

#### 表 6-1 Pin Functions (continued)

|     | (2)                    |                                                                                     | 支 6-1. Pin Functio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ons (contin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ueu)                                               |                                                    |                                                                |                                                                |

|-----|------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|

| _   | TYPE <sup>(2)</sup>    | _                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    | DESCF                                              | RIPTION                                                        |                                                                |

| NO. |                        | SIAIL                                                                               | JUPPLI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |                                                    |                                                                |                                                                |

| C3  | I                      | Internal pull-<br>down 1 M Ω<br>typical<br>(disabled<br>after reset) <sup>(1)</sup> | VDD1V8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I <sup>2</sup> C Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Dovino                                             | Low                                                | SDA See 表 6-4 for more details                                 | Mode<br>Non-I <sup>2</sup> C<br>USB<br>Repeater                |

| В3  | I/O                    | Hi-Z <sup>(1)</sup>                                                                 | VDD1V8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Bidirectional<br>1 <sup>2</sup> C data<br>Open drain<br>I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Mode<br>Matrix                                     | High                                               | Low                                                            | Non-I <sup>2</sup> C<br>UART<br>mode<br>Repeater               |

|     |                        |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    | High                                               | High                                                           | I <sup>2</sup> C<br>Enabled                                    |

| C2  | I/O                    | Internal pull-down 1 M $\Omega$ typical (disabled after reset)                      | VDD1V8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul> <li>In I<sup>2</sup>C mode GPIO2 will be an open drain active low level interrupt output. Connect GPIO2 to input of APU and a pull-up resistor to use interrupt features</li> <li>In non I<sup>2</sup>C mode GPIO2 defaults to USB configuration input at power up reset.</li> <li>When a pull-up resistor is used to set high input, ensure VIH is met accounting for internal pull down as small as 500 k Ω</li> <li>GPIO2 is an open-drain output after reset and can be left floating when not used.</li> </ul>                           |                                                    |                                                    |                                                                |                                                                |

| В1  | I/O                    | Internal pull-<br>down 1 M Ω<br>typical<br>(disabled<br>after reset) <sup>(1)</sup> | VDD1V8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul> <li>Defaults to an input mode at power up reset. RESETB assertion and de-assertion or soft reset will revert GPIO0 to input mode</li> <li>In I²C mode GPIO0 will default to control Carkit UART mode: active low to enable Carkit UART mode. Default Carkit UART direction is DP → eDP (RX) and eDN → DN (TX). GPIO0 must be pulled up to be in USB repeater mode.</li> <li>In non I²C mode GPIO0 defaults to USB configuration input at power up reset.</li> <li>When a pull-up resistor is used to set high input, ensure VIH is</li> </ul> |                                                    |                                                    |                                                                | mode RT mode: kit UART PIO0 must on input at                   |

| C1  | I/O                    | Internal pull-<br>down 1 M Ω<br>typical<br>(disabled<br>after reset) <sup>(1)</sup> | VDD1V8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul> <li>Defaults to an input mode at power up reset. RESETB assertion and de-assertion or soft reset will revert GPIO1 to input mode</li> <li>In I<sup>2</sup>C mode GPIO1 defaults to debug input</li> <li>In non I<sup>2</sup>C mode GPIO1 defaults to USB Configuration input at power up reset.</li> <li>When a pull-up resistor is used to set high input, ensure VIH is met accounting for internal pull down as small as 500 k Ω</li> </ul>                                                                                                |                                                    |                                                    |                                                                |                                                                |

| A2  | I/O                    | Hi-Z                                                                                | VDD1V8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | eUSB2 port D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | )_                                                 |                                                    |                                                                |                                                                |

| A1  | I/O                    | Hi-Z                                                                                | VDD1V8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | eUSB2 port D+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    |                                                    |                                                                |                                                                |

| E2  | I/O                    | Hi-Z                                                                                | VDD3V3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | USB port D-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |                                                    |                                                                |                                                                |

| E1  | I/O                    | Hi-Z                                                                                | VDD3V3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | USB port D+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |                                                    |                                                                |                                                                |

|     | C2  B3  C1  A2  A1  E2 | NO.  C3   I                                                                         | NO.         TYPE <sup>(2)</sup> REST STATE           NO.         Internal pull-down 1 M Ω typical (disabled after reset)(1)           B3         I/O         Hi-Z <sup>(1)</sup> B1         I/O         Internal pull-down 1 M Ω typical (disabled after reset)           B1         I/O         Internal pull-down 1 M Ω typical (disabled after reset)(1)           C1         I/O         Internal pull-down 1 M Ω typical (disabled after reset)(1)           A2         I/O         Hi-Z           A1         I/O         Hi-Z           E2         I/O         Hi-Z | NO.   TYPE(2)   REST STATE   ASSOCIATED ESD SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NO.   TYPE(2)   REST STATE   ASSOCIATED ESD SUPPLY | NO.   TYPE(2)   REST STATE   ASSOCIATED ESD SUPPLY | NO.   TYPE <sup>(2)</sup>   REST STATE   ASSOCIATED ESD SUPPLY | NO.   TYPE <sup>(2)</sup>   REST STATE   ASSOCIATED ESD SUPPLY |

<sup>(1)</sup> When configured as an input but not actively driven, use 1 M  $\Omega$  external pull-down to strap low. (2) I = input, I/O = input or output, PWR= power, GND = ground

# 表 6-2. Pin Configuration for Device Mode

| Device Mode                            | SCL (C3)                                            | SDA (B3)                               | GPIO0 (B1)                                                                                                   | GPIO1 (C1)                                                              | GPIO2 (C2)                                                                                                                        |  |  |

|----------------------------------------|-----------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

| I <sup>2</sup> C Mode                  | Pull-up<br>Input sampled at<br>reset                | Pull-up<br>Input sampled at<br>reset   | Default to Input  Low = UART  Mode  High = USB  repeater mode  Function can be reconfigured through register | Default to Input<br>Function can be<br>reconfigured through<br>register | Default to Open drain<br>output (can be left<br>floating when not<br>used)<br>Function can be<br>reconfigured through<br>register |  |  |

| Non I <sup>2</sup> C UART mode         | Pull-up<br>Input sampled at<br>reset                | Pull-down<br>Input sampled at<br>reset | Default to Input  Low = UART transfer enabled  High = UART transfer disabled                                 | High-Z (can be left floating)                                           | High-Z (can be left<br>floating)                                                                                                  |  |  |

| Non I <sup>2</sup> C USB repeater mode | Pull-down<br>Input sampled at<br>reset<br>See 表 6-4 | See 表 6-4                              | Def                                                                                                          | ault input sampled at reset.<br>See 表 6-3                               |                                                                                                                                   |  |  |

Product Folder Links: TUSB2E11

### 表 6-3. Pin Configuration for USB PHY Tuning without I<sup>2</sup>C

| GPIO2    | GPIO1    | GPIO0    | Equivalent<br>series<br>resistance<br>(ESR)<br>between<br>repeater<br>and USB<br>connector | U_EQ_P1<br>setting | U_HS_TX_<br>AMPLITUD<br>E_P1<br>setting | U_HS_TX_<br>PRE_EMPH<br>ASIS_P1<br>setting | U_SQUELC<br>H_THRESH<br>OLD_P1<br>setting | U_DISCON<br>NECT_THR<br>ESHOLD_P<br>1 setting | HS Term   |            |           |           |            |    |

|----------|----------|----------|--------------------------------------------------------------------------------------------|--------------------|-----------------------------------------|--------------------------------------------|-------------------------------------------|-----------------------------------------------|-----------|------------|-----------|-----------|------------|----|

|          |          |          | Ω                                                                                          | dB                 | mV                                      | dB                                         | mV                                        | mV                                            | Ω         |            |           |           |            |    |

| Float    | Float    | Float    | 2.5                                                                                        | 0.06               | 840                                     | 0.5                                        | 104                                       | 625                                           | 45        |            |           |           |            |    |

| Float    | Float    | Float    | 2.5                                                                                        | (3' b000)          | (4' b0101)                              | (3' b000)                                  | (3' b100)                                 | (4' b0101)                                    | 45        |            |           |           |            |    |

| Float    | Float    | Pull-Up  | 5                                                                                          | 0.06               | 880                                     | 0.9                                        | 98                                        | 645                                           | 45        |            |           |           |            |    |

| Float    | Float    | Full-Op  | 5                                                                                          | (3' b000)          | (4' b0111)                              | (3' b001)                                  | (3' b101)                                 | (4' b0110)                                    | 45        |            |           |           |            |    |

| Float    | Pull-Up  | Float    | 7.5                                                                                        | 0.58               | 900                                     | 0.9                                        | 98                                        | 645                                           | 45        |            |           |           |            |    |

| Float    | Pull-Op  | Float    | 7.5                                                                                        | (3' b001)          | (4' b1000)                              | (3' b001)                                  | (3' b101)                                 | (4' b0110)                                    | 45        |            |           |           |            |    |

| Float    | Pull-Up  | Dull Lin | 10                                                                                         | 1.09               | 920                                     | 0.9                                        | 98                                        | 685                                           | 45        |            |           |           |            |    |

| Float    | Full-Op  | Pull-Up  | Full-Op                                                                                    | i dii-Op           | 10                                      | (3' b010)                                  | (4' b1001)                                | (3' b001)                                     | (3' b101) | (4' b1000) | 45        |           |            |    |

| Dull Lin | Floor    | Floor    | 12.5                                                                                       | 1.56               | 940                                     | 1.2                                        | 91                                        | 685                                           | 45        |            |           |           |            |    |

| Pull-Up  | Float    | Float    | Float                                                                                      | Fioat              | Fioat                                   | Float                                      | Float                                     | 12.5                                          | (3' b011) | (4' b1010) | (3' b010) | (3' b110) | (4' b1000) | 45 |

| Pull-Up  | Float    | Dull Lin | 15                                                                                         | 2.26               | 980                                     | 1.2                                        | 91                                        | 685                                           | 45        |            |           |           |            |    |

| Full-Op  | Float    | Pull-Up  | Pull-Up                                                                                    | Pull-Op            | Pull-Up                                 | Pull-Up                                    | Pull-Up                                   | 10                                            | (3' b100) | (4' b1100) | (3' b010) | (3' b110) | (4' b1000) | 40 |

| Pull-Up  | Pull-Up  | Float    | 17.5                                                                                       | 2.67               | 1000                                    | 1.7                                        | 91                                        | 685                                           | 45        |            |           |           |            |    |

| i dil-Op | i dii-Op | Float    | 17.5                                                                                       | (3' b101)          | (4' b1101)                              | (3' b011)                                  | (3' b110)                                 | (4' b1000)                                    | 40        |            |           |           |            |    |

| Pull-Up  | Pull-Up  | Dull-Hr  | 20                                                                                         | 2.67               | 1020                                    | 1.7                                        | 85                                        | 705                                           | 12.75     |            |           |           |            |    |

| I dil-Op | rull-Up  | Pull-Up  | 20                                                                                         | (3' b101)          | (4' b1110)                              | (3' b011)                                  | (3' b111)                                 | (4' b1001)                                    | 42.75     |            |           |           |            |    |

# 表 6-4. Pin Configuration for Battery Charging in non I<sup>2</sup>C Mode

| Device Mode                            |                                                             | 4. Fill Collingi                                                                                                     |                                                                                                                  | Repeater State | Charger<br>Detection<br>Status     | VBUS Control<br>Output                                                                                                       |                                                               |

|----------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

|                                        | SCL (C3)                                                    | SDA (B3)                                                                                                             | Unconfigured                                                                                                     | Host Repeater  | Peripheral<br>Repeater             | {GPIO2,<br>GPIO1}                                                                                                            | GPIO0                                                         |

| Non I <sup>2</sup> C USB repeater mode | Pull-down resistor to ground 0 to 160 Ω                     | Input Low = BC 1.2 disabled High = BC 1.2 enabled                                                                    | When BC 1.2 is<br>enabled,<br>charger<br>detection                                                               | N/A            | N/A                                | 2' b00: No charger detected     2' b01: CDP or                                                                               |                                                               |

| Non I <sup>2</sup> C USB repeater mode | Pull-down resistor to ground 1.5 k $\Omega$ to 2 k $\Omega$ | Input VBUS_Valid input: use a voltage divider to reduce VBUS voltage to appropriate VIH for 1.8 V or 1.2 V I/O mode. | When<br>VBUS_valid is<br>high enable<br>charger<br>detection                                                     | N/A            | Charger<br>detection is<br>enabled | DCP charger detected 2' b10: DCP (1.5A) or Divider Mode (2.1A) charger detected 2' b11: Divider Mode (2.4A) charger detected | N/A                                                           |

| Non I <sup>2</sup> C USB repeater mode | Pull-down resistor to ground 3.4 kΩ to 3.96 kΩ              | Input Low = BC 1.2 disabled High = BC 1.2 enabled                                                                    | When BC 1.2 is<br>enabled,<br>advertise<br>charging BC 1.2<br>DCP                                                | Advertise CDP  | N/A                                | N/A                                                                                                                          | Active High<br>Push-Pull<br>output for VBUS<br>switch Control |

| Non I <sup>2</sup> C USB repeater mode | Pull-down<br>resistor to<br>ground<br>7.5 k Ω to 11<br>k Ω  | Input Low = BC 1.2 disabled High = BC 1.2 enabled                                                                    | When BC 1.2 is<br>enabled,<br>advertise<br>charging (auto<br>cycle between<br>BC 1.2 DCP<br>and Divider<br>mode) | Advertise CDP  | N/A                                | N/A                                                                                                                          | • High = VBUS ON • Low = VBUS OFF                             |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                             |                                                                                                    | MIN   | MAX  | UNIT |

|-----------------------------|----------------------------------------------------------------------------------------------------|-------|------|------|

| Supply voltage range        | V <sub>DD3V3</sub>                                                                                 | - 0.3 | 4.32 | V    |

| Analog Supply voltage range | V <sub>DD1V8</sub>                                                                                 | - 0.3 | 2.1  | V    |

| Voltage range               | DP, DN, (with OVP enabled), 1000 total number of short events and cumulative duration of 1000 hrs. | - 0.3 | 6    | V    |

| Voltage range               | eDP, eDN                                                                                           | - 0.3 | 1.6  | V    |

| Voltage range               | RESETB, GPIO0, GPIO1, GPIO2, SCL, SDA                                                              | - 0.3 | 2.1  | V    |

| Junction temperature        | T <sub>J(max)</sub>                                                                                |       | 125  | °C   |

| Storage temperature         | T <sub>stg</sub>                                                                                   | - 65  | 150  | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute maximum ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If briefly operating outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not sustain damage, but it may not be fully functional. Operating the device in this manner may affect device reliability, functionality, performance, and shorten the device lifetime.

#### 7.2 ESD Ratings

|                    |                         |                                                                                     | VALU<br>E | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------|-----------|------|

| \/                 | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>         | ±1500     | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JS-002, all pins <sup>(2)</sup> | ±500      | v    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.3 Recommended Operating Conditions

|                    |                                                     | MIN  | NOM | MAX  | UNIT |

|--------------------|-----------------------------------------------------|------|-----|------|------|

| V <sub>DD3V3</sub> | Supply voltage (VDD3V3)                             | 3.0  | 3.3 | 3.6  | V    |

| V <sub>DD1V8</sub> | Analog Supply voltage (VDD1V8)                      | 1.62 | 1.8 | 1.98 | V    |

| V_I2C_Pullup       | I2C and GPIO open drain Bus Voltage (1.2 V Variant) | 1.08 | 1.2 | 1.32 | V    |

| V_I2C_Pullup       | I2C and GPIO open drain Bus Voltage (1.8 V Variant) | 1.62 | 1.8 | 1.98 | V    |

| USB<br>Voltage     | DP, DN                                              | 0    |     | 3.6  | V    |

| eUSB2<br>voltage   | eDP, eDN                                            | 0    |     | 1.32 | V    |

| Digital voltage    | GPIO0, GPIO1, GPIO2, SCL, SDA (1.8 V Variant)       | 0    |     | 1.98 | V    |

| Digital voltage    | GPIO0, GPIO1, GPIO2, SCL, SDA (1.2 V Variant)       | 0    |     | 1.32 | V    |

| RESETB             | RESETB (1.2 V or 1.8 V Variant)                     | 0    |     | 1.98 | V    |

| T <sub>A</sub>     | Operating free-air temperature                      | -20  |     | 85   | °C   |

| TJ                 | Junction temperature                                | -20  |     | 105  | °C   |

| T <sub>CASE</sub>  | Case temperature                                    | -20  |     | 105  | °C   |

|                  |                                 | , , , , , , , , , , , , , , , , , , , |     |     |     |      |

|------------------|---------------------------------|---------------------------------------|-----|-----|-----|------|

|                  |                                 |                                       | MIN | NOM | MAX | UNIT |

| T <sub>PCB</sub> | PCB temperature (1 mm away from | n the device)                         | -20 |     | 92  | °C   |

#### 7.4 Thermal Information

|                        |                                              | TUSB2E11    |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | YCG (DSBGA) | UNIT |

|                        |                                              | 15 PINS     |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 90.5        | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 0.6         | °C/W |

| R <sub>θ JB</sub>      | Junction-to-board thermal resistance         | 22.9        | °C/W |

| $\Psi$ JT              | Junction-to-top characterization parameter   | 0.4         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 22.9        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.5 Electrical Characteristics

|                       | PARAMETER                                                                           | TEST CONDITIONS                                                                                                                                                                                                            | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| POWER                 |                                                                                     |                                                                                                                                                                                                                            |     |     |     |      |

| P <sub>WC_1V8</sub>   | Absolute worst case peak power consumption (VDD1V8 only) for power supply budgeting | I2C interface active, GPIOs in output mode, repeater in HS mode with USB transmitting, maximum RX EQ, max TX VOD and PE settings, maximum transition density. T <sub>A</sub> = −20°C to 85°C.                              |     |     | 280 | mW   |

| P <sub>WC_3V3</sub>   | Absolute worst case peak power consumption (VDD3V3 only) for power supply budgeting | I2C interface active, GPIOs in output mode, repeater in HS mode with USB transmitting, maximum RX EQ, max TX VOD and PE settings, maximum transition density. T <sub>A</sub> = -20°C to 85°C.                              |     |     | 30  | mW   |

| P <sub>WCFS_3V3</sub> | Absolute worst case peak power consumption (VDD3V3 only) for power supply budgeting | I2C interface active, GPIOs in output mode, repeater in FS mode with USB Asynchronous traffic. T <sub>A</sub> = -20°C to 85°C.                                                                                             |     |     | 75  | mW   |

| P <sub>HS_IOC</sub>   | USB Audio ISOC High-speed                                                           | Maximum TX Vod/Maximum TX PE for both USB and eUSB2. Averaged over 8 ms and only 1 uFrame with data packet. Toff threshold = 1/32. Host Peripheral Mode.                                                                   |     | 35  |     | mW   |

| P <sub>PD</sub>       | Powered down                                                                        | Device powered, RESETB=Low, $T_A$ =25°C, (DP/DN Voltage $\leq$ VDD3V3).                                                                                                                                                    |     |     | 9   | μW   |

| P <sub>Disabled</sub> | Disabled                                                                            | Device powered, I2C/GPIO interfaces functional but idle, repeater is disabled and put into the lowest power state and non-functional. $T_A$ =25°C, (DP/DN Voltage $\leq$ VDD3V3).                                          |     | 43  | 95  | μW   |

| P <sub>Detach</sub>   | USB unconnected                                                                     | I2C/GPIO interfaces idle, repeater is connected to a eUSB2 PHY and waiting for a USB attach event. $T_A$ = 25°C, (DP/DN Voltage $\leq$ VDD3V3)                                                                             |     | 43  | 85  | μW   |

| $P_{Suspend}$         | L2 Suspend (host mode)                                                              | I2C/GPIO interfaces idle, USB link is in L2, repeater is monitoring for a resume/ remote wake event. T <sub>A</sub> = 25°C, (DP/DN Voltage ≤ VDD3V3). In peripheral mode additional current is present due the DP pull up. |     | 45  | 85  | μW   |

over operating free-air temperature range (unless otherwise noted)

|                             | PARAMETER                                   | TEST CONDITIONS                                                                                                                                                                                                  | MIN   | TYP | MAX   | UNIT |

|-----------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| $P_{Sleep}$                 | L1 Sleep                                    | I2C/GPIO interfaces idle, repeater is supporting a USB connection, USB link is in L1 (host exists L1 every 1 ms) and repeater is monitoring for a L1 exit event. T <sub>A</sub> = 25°C, (DP/DN Voltage ≤ VDD3V3) |       | 2.3 | 5     | mW   |

| P <sub>LS_Active</sub>      | Low Speed Active                            | I2C/GPIO interfaces idle, repeater in LS mode, maximum transition density. T <sub>A</sub> = 85°C.                                                                                                                |       | 7.2 | 24    | mW   |

| PFS1_Active                 | Full Speed Active (ASYNC Traffic)           | I2C/GPIO interfaces idle, repeater in FS mode, maximum transition density. T <sub>A</sub> = 85°C.                                                                                                                |       | 45  | 80    | mW   |

| P <sub>FS2_Active</sub>     | Full Speed Active (ISO Traffic)             | I2C/GPIO interfaces idle, repeater in FS mode, maximum transition density. T <sub>A</sub> = 85°C.                                                                                                                |       | 9   | 24    | mW   |

| P <sub>HS_Idle_Host</sub>   | High Speed Idle (Host mode)                 | L0.Idle. TA = 85°C. (Typical at 25°C).                                                                                                                                                                           |       | 26  | 70    | mW   |

| P <sub>HS_Idle_Periph</sub> | High Speed Idle (Peripheral mode)           | L0.Idle. TA = 85°C. (Typical at 25°C).                                                                                                                                                                           |       | 108 | 200   | mW   |

| DIGITAL INPU                | JTS                                         |                                                                                                                                                                                                                  |       |     |       |      |

| V <sub>IH</sub>             | High level input voltage                    | GPIO0, GPIO1, GPIO2 (1.2 V Variant)                                                                                                                                                                              | 0.702 |     |       | V    |

| V <sub>IH</sub>             | High level input voltage                    | GPIO0, GPIO1, GPIO2 (1.8 V Variant)                                                                                                                                                                              | 1.053 |     |       | V    |

| V <sub>IL</sub>             | Low-level input voltage                     | GPIO0, GPIO1, GPIO2 (1.2 V Variant)                                                                                                                                                                              |       |     | 0.462 | V    |

| $V_{IL}$                    | Low-level input voltage                     | GPIO0, GPIO1, GPIO2 (1.8 V Variant)                                                                                                                                                                              |       |     | 0.693 | V    |

| V <sub>IL</sub>             | Low-level input voltage                     | RESETB                                                                                                                                                                                                           |       |     | 0.35  | V    |

| V <sub>IH</sub>             | High level input voltage                    | RESETB                                                                                                                                                                                                           | 0.75  |     |       | V    |

| I <sub>IH</sub>             | High level input current                    | V <sub>IH</sub> = 1.98 V, VDD3V3=3.0 V or 0 V,<br>VDD1V8=1.62 V or 0 V<br>RESETB, GPIO0, GPIO1                                                                                                                   |       |     | 0.5   | μΑ   |

| I <sub>IL</sub>             | Low level input current                     | V <sub>IL</sub> = 0 V, VDD3V3=3.0 V or 0 V,<br>VDD1V8=1.62 V or 0 V<br>RESETB, GPIO0, GPIO1                                                                                                                      |       |     | 0.5   | μΑ   |

| DIGITAL OUT                 | PUTS                                        |                                                                                                                                                                                                                  |       |     |       |      |

| V <sub>OH</sub>             | High level output voltage                   | GPIO0, GPIO1, GPIO2, push-pull I/O mode (I <sub>OH</sub> = 20 µA and maximum 3 pF C <sub>load)</sub> (1.2 V Variant)                                                                                             | 0.81  |     |       | V    |

| V <sub>OH</sub>             | High level output voltage                   | GPIO0, GPIO1, GPIO2, push-pull I/O mode (I <sub>OH</sub> = 20 μA and maximum 3 pF C <sub>load)</sub> (1.8 V Variant)                                                                                             | 1.21  |     |       | V    |

| V <sub>OL</sub>             | Low level output voltage                    | GPIO0, GPIO1, GPIO2, push-pull I/O mode (I <sub>OL</sub> = 1 mA) (1.2 V Variant)                                                                                                                                 |       |     | 0.25  | V    |

| V <sub>OL</sub>             | Low level output voltage                    | GPIO0, GPIO1, GPIO2, push-pull I/O mode (I <sub>OL</sub> = 1 mA) (1.8 V Variant)                                                                                                                                 |       |     | 0.35  | V    |

| I <sub>OL_PP</sub>          | Low level output current in push-pull mode  | GPIO0, GPIO1, GPIO2 (1.2 V Variant),<br>VOL=0.4 V                                                                                                                                                                | 2.5   | 4   | 5.6   | mA   |

| I <sub>OL_PP</sub>          | Low level output current in push-pull mode  | GPIO0, GPIO1, GPIO2 (1.8 V Variant),<br>VOL=0.4 V                                                                                                                                                                | 4     | 6   | 8     | mA   |

| Іон_рр                      | High level output current in push-pull mode | GPIO0, GPIO1, GPIO2, push-pull I/O mode, VOH=0.9 V (1.2 V Variant)                                                                                                                                               | 22    |     |       | μΑ   |

| I <sub>OH_PP</sub>          | High level output current in push-pull mode | GPIO0, GPIO1, GPIO2, push-pull I/O mode, VOH=0.9 V (1.8 V Variant)                                                                                                                                               | 50    |     |       | μΑ   |

| I2C (SDA, SC                | L)                                          |                                                                                                                                                                                                                  |       |     |       |      |

| V <sub>IL</sub>             | Low level input voltage, 1.2 V variant      | SDA, SCL, V <sub>I2C Pullup</sub> = 1.08 V                                                                                                                                                                       |       |     | 0.387 | V    |

English Data Sheet: SLLSFI4

|                        | PARAMETER                                                              | TEST CONDITIONS                                                                                                  | MIN   | TYP | MAX   | UNIT                |

|------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|-----|-------|---------------------|

| V <sub>IL</sub>        | Low level input voltage, 1.8 V variant                                 | SDA, SCL, V <sub>I2C_Pullup</sub> = 1.96 V                                                                       |       |     | 0.588 | V                   |

| V <sub>IH</sub>        | High level input voltage, 1.2 V variant                                | SDA, SCL, V_I2C_Pullup = 1.08 V                                                                                  | 0.833 | ,   |       | V                   |

| V <sub>IH</sub>        | High level input voltage, 1.8 V variant                                | SDA, SCL, V_I2C_Pullup = 1.96 V                                                                                  | 1.372 | ,   |       | V                   |

| V <sub>HYS</sub>       | Input hysteresis, 1.2 V variant                                        | V_I2C_Pullup = 1.08 V                                                                                            | 0.020 |     |       | V                   |

| V <sub>HYS</sub>       | Input hysteresis, 1.8 V variant                                        | V_I2C_Pullup = 1.96 V                                                                                            | 0.098 |     |       | V                   |

| I <sub>IH</sub>        | High level input leakage current                                       | V <sub>IH</sub> = 1.98 V                                                                                         |       |     | 0.5   | μA                  |

| I <sub>IL</sub>        | Low level input leakage current                                        | V <sub>IL</sub> = 0 V                                                                                            |       | ,   | 0.5   | μA                  |

| V <sub>OL</sub>        | Low level output voltage (1 $k\Omega$ pull up), 1.2 V variant          | I <sub>OL</sub> = 2.5 mA, V_I2C_Pullup = 1.08 V                                                                  |       |     | 0.2   | V                   |

| V <sub>OL</sub>        | Low level output voltage (1 k $\Omega$ pull up), 1.8V variant          | I <sub>OL</sub> = 2.5 mA, V_I2C_Pullup = 1.96 V                                                                  |       |     | 0.3   | V                   |

| I <sub>OL</sub>        | Open drain drive strength, 1.2 V Variant                               | VOL = 0.4 V                                                                                                      | 1.6   | 2.4 | 3.0   | mA                  |

| I <sub>OL</sub>        | Open drain drive strength, 1.8 V Variant                               | VOL = 0.4 V                                                                                                      | 8     | 10  | 12.6  | mA                  |

| UART I/O               |                                                                        |                                                                                                                  |       |     |       |                     |

| V <sub>OLI</sub>       | Internal output low                                                    | Internal UART output (eDP/eDN) 1.2 V signaling                                                                   |       |     | 0.1   | V                   |

| V <sub>OHI</sub>       | Internal output high                                                   | Internal UART output (eDP/eDN) 1.2 V signaling                                                                   | 0.918 |     | 1.32  | V                   |

| V <sub>ILI</sub>       | Internal input low                                                     | Internal UART input (eDP/eDN) 1.2 V signaling                                                                    | - 0.1 |     | 0.399 | V                   |

| V <sub>IHI</sub>       | Internal input high                                                    | Internal UART input (eDP/eDN) 1.2 V signaling                                                                    | 0.819 |     | 1.386 | V                   |

| V <sub>OLE</sub>       | External output low                                                    | External UART output (DP/DN) 3.3 V signaling                                                                     | 0     |     | 0.3   | V                   |

| V <sub>OHE</sub>       | External output high                                                   | External UART output (DP/DN) 3.3 V signaling                                                                     | 2.8   |     | 3.6   | V                   |

| V <sub>ILE</sub>       | External input low                                                     | External UART input (DP/DN) 3.3 V signaling                                                                      |       |     | 0.8   | V                   |

| $V_{IHE}$              | External input high                                                    | External UART input (DP/DN) 3.3 V signaling                                                                      | 2     |     |       | V                   |

| USB (DP, DI            | ۷)                                                                     |                                                                                                                  |       |     |       |                     |

| Z <sub>inp_Dx</sub>    | Impedance to GND, no pull up or pull down                              | Vin=3.6 V, V <sub>DD3V3</sub> =3.0 V, <i>Input</i> Characteristics <sup>(1)</sup>                                | 390   |     |       | $\mathbf{k} \Omega$ |

| C <sub>IO_Dx</sub>     | Capacitance to GND                                                     | Measured with VNA at 240 MHz, Driver Hi-Z                                                                        |       |     | 10    | pF                  |

| R <sub>PUI</sub>       | Bus pull-up resistor on upstream facing port (idle)                    | High-speed Device Speed Identification <sup>(1)</sup>                                                            | 0.92  | 1.1 | 1.475 | kΩ                  |

| R <sub>PUR</sub>       | Bus pull-up resistor on upstream facing port (receiving)               | High-speed Device Speed Identification <sup>(1)</sup>                                                            | 1.525 | 2.2 | 2.99  | kΩ                  |

| R <sub>PD</sub>        | Bus pull-down resistor on downstream facing port                       | High-speed Device Speed Identification <sup>(1)</sup>                                                            | 14.35 | 19  | 24.6  | kΩ                  |

| V <sub>HSTERM</sub>    | Termination voltage in highspeed                                       | The output voltage in the high-speed idle state, <i>High-speed Input Characteristics</i> <sup>(1)</sup>          | - 10  |     | 10    | mV                  |

| USB TERMI              | NATION                                                                 |                                                                                                                  |       |     |       |                     |

| Z <sub>HSTERM_</sub> P | Driver Output Resistance (which also serves as high speed termination) | (VOH= 0 to 600 mV) Full-speed (12 Mb/s) Driver Characteristics <sup>(1)</sup> , Default, U_HS_TERM_Px setting 01 | 40.6  | 45  | 49.4  | Ω                   |

|                       | PARAMETER                                                              | TEST CONDITIONS                                                                                                                                                                                                                        | MIN  | TYP | MAX  | UNIT |

|-----------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| Z <sub>HSTERM_N</sub> | Driver Output Resistance (which also serves as high speed termination) | (VOH= 0 to 600 mV) Full-speed (12<br>Mb/s) Driver Characteristics <sup>(1)</sup> , Default,<br>U_HS_TERM_Px setting 01                                                                                                                 | 40.6 | 45  | 49.4 | Ω    |

| USB INPUT             | LEVELS LS/FS                                                           |                                                                                                                                                                                                                                        |      |     | L    |      |

| V <sub>IH</sub>       | High (driven)                                                          | Receiver Characteristics <sup>(1)</sup> (measured at the connector)                                                                                                                                                                    | 2    |     |      | V    |

| $V_{IHZ}$             | High (floating)                                                        | Receiver Characteristics <sup>(1)</sup> (HOST downstream port pull-down resistor enabled and external device pull up 1.5 k $\Omega$ ± 5% to 3.0-3.6 V)                                                                                 | 2.7  |     | 3.6  | V    |

| V <sub>IL</sub>       | Low                                                                    | Receiver Characteristics <sup>(1)</sup>                                                                                                                                                                                                |      |     | 0.8  | V    |

| V <sub>DI</sub>       | Differential Input Sensitivity (hysteresis is off)                     | (D+)-(D-) ; Differential Input Sensitivity<br>Range for Low-/full-speed <sup>(1)</sup> ; (measured<br>at connector) V <sub>CM</sub> =0.8 V to 2.0 V                                                                                    |      |     | 0.2  | V    |

| USB OUTPL             | JT LEVELS LS/FS                                                        |                                                                                                                                                                                                                                        |      |     | 1    |      |

| V <sub>OL</sub>       | Low                                                                    | USB Driver Characteristics <sup>(1)</sup> , (measured at connector with RL of 1.425 k $\Omega$ to 3.6 V.)                                                                                                                              | 0    |     | 0.3  | V    |

| V <sub>OH</sub>       | High (Driven)                                                          | USB Driver Characteristics $^{(1)}$ , (measured at the connector with RL of 14.25 k $\Omega$ to GND.)                                                                                                                                  | 2.8  |     | 3.6  | V    |

| Z <sub>FSTERM</sub>   | Driver Series Output Resistance                                        | USB Driver Characteristics <sup>(1)</sup> , measured it during VOL or VOH                                                                                                                                                              | 28   |     | 44   | Ω    |

| V <sub>CRS2</sub>     | Output Signal Crossover Voltage                                        | Measured as in <i>Data Signal Rise and</i> Fall Time <sup>(1)</sup> , excluding the first transition from the Idle state. With external 1.5 $k\Omega$ pull up on DP to 3.0 V                                                           | 1.3  |     | 2    | V    |

| V <sub>CRS</sub>      | Output Signal Crossover Voltage                                        | Measured as in <i>Data Signal Rise and</i> Fall Time <sup>(1)</sup> , excluding the first transition from the Idle state                                                                                                               | 1.3  |     | 2    | V    |

| USB INPUT             | LEVELS HS                                                              |                                                                                                                                                                                                                                        |      |     | '    |      |

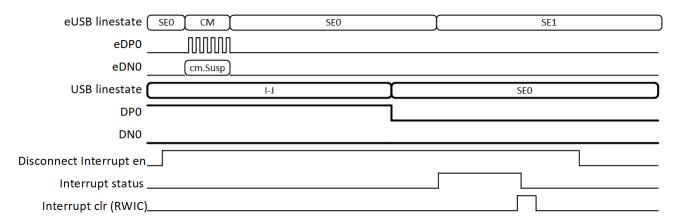

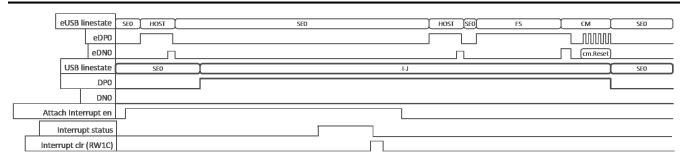

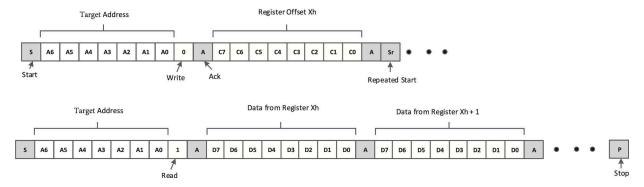

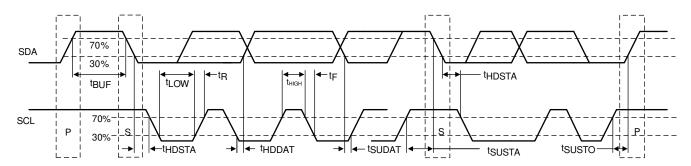

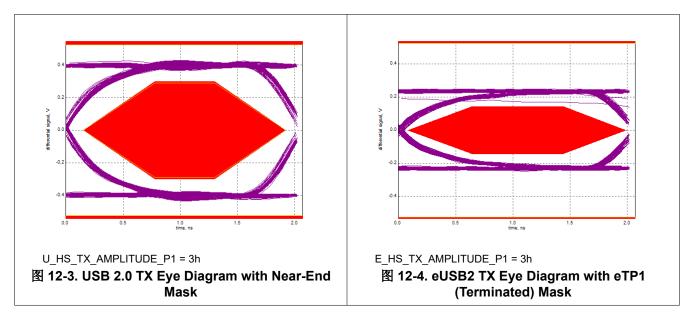

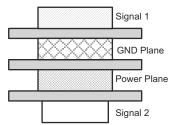

| $V_{HSSQ}$            | High-speed squelch/no-squelch detection threshold                      | Full-/High-speed Signaling Level <sup>11</sup> , specification refers to peak differential signal amplitude), measured at 240 MHz with increasing amplitude, U_SQUELCH_THRESHOLD_Px setting 011, V <sub>CM</sub> = -50 mV to 500 mV    | 111  | 128 | 161  | mV   |