# 具有有源整流和负载突降保护功能的 LM7481-Q1 理想二极管控制器

# 1 特性

- 符合面向汽车应用的 AEC-Q100 标准

- 器件温度等级 1:

- 40°C 至 +125°C 环境工作温度范围

- 器件 HBM ESD 分类等级 2

- 器件 CDM ESD 分类等级 C4B

- 3V 至 65V 输入范围

- 反向输入保护低至 65V

- 驱动外部背对背 N 沟道 MOSFET

- 9.1mV 阳极至阴极正向压降调节下,理想二极管正 常运行

- 低反向检测阈值 (-4mV), 能够快速响应 (0.5µs)

- 高达 200KHz 的有源整流

- 60mA 峰值栅极 (DGATE) 导通电流

- 2.6A 峰值 DGATE 关断电流

- 集成 3.8mA 电荷泵

- 可调节过压保护

- 2.87µA 低关断电流(EN/UVLO = 低电平)

- 2.6A 峰值 DGATE 关断电流

- 采用合适的 TVS 二极管,符合汽车 ISO7637 瞬态

- 采用节省空间的 12 引脚 WSON 封装

#### 2 应用

- 汽车电池保护

- ADAS 域控制器

- 音响主机

- 高端音响

- 用于冗余电源的有源 ORing

具有开关输出的理想二极管

### 3 说明

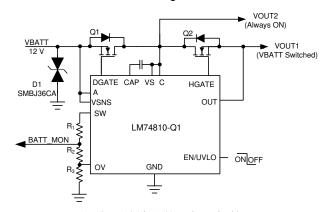

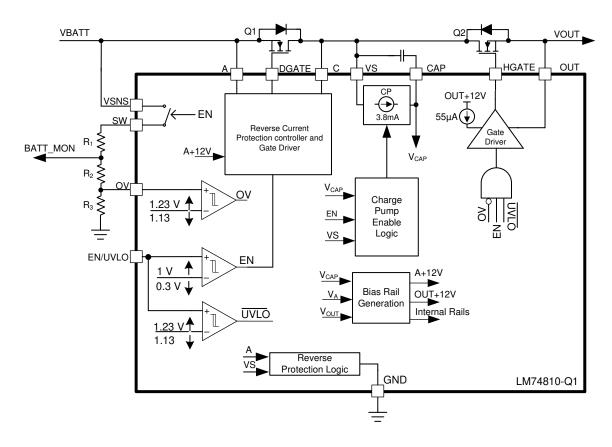

LM74810-Q1 理想二极管控制器可驱动和控制外部背 对背 N 沟道 MOSFET,从而模拟具有电源路径开/关控 制和过压保护的理想二极管整流器。3V至 65V 的宽输 入电源电压可保护和控制 12V 和 24V 汽车类电池供电 的 ECU。该器件可以承受并保护负载免受低至 - 65V 的负电源电压的影响。集成的理想二极管控制器 (DGATE) 可驱动第一个 MOSFET 来代替肖特基二极 管,以实现反向输入保护和输出电压保持。具有 60mA 峰值栅极拉电流驱动器级以及短导通和关断延迟时间的 3.8mA 强电荷泵可确保快速的瞬态响应,从而确保在 汽车测试 (如 ISO16750 或 LV124 )期间实现稳健、 高效的 MOSFET 开关性能,在汽车测试中 ECU 会收 到输入短时中断以及频率高达 200KHz 的交流叠加输 入信号。在电源路径中使用了第二个 MOSFET 的情况 下,该器件允许负载断开(开/关控制)并使用 HGATE 控制提供过压保护。该器件具有可调节过压切断保护功 能,以提供负载突降保护。

#### 器件信息(1)

| 器件型号       | 封装        | 封装尺寸(标称值)     |

|------------|-----------|---------------|

| LM74810-Q1 | WSON (12) | 3.0mm x 3.0mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附

ISO16750、LV124 交流叠加性能

# **Table of Contents**

| 1 特性                                 | 1 | 9 Application and Implementation                     | 18                |

|--------------------------------------|---|------------------------------------------------------|-------------------|

| 2 应用                                 |   | 9.1 Application Information                          | 18                |

| 3 说明                                 |   | 9.2 Typical 12-V Reverse Battery Protection          |                   |

| 4 Revision History                   |   | Application                                          | 18                |

| 5 Pin Configuration and Functions    |   | 9.3 Do's and Don'ts                                  |                   |

| 6 Specifications                     |   | 10 Power Supply Recommendations                      | <mark>27</mark>   |

| 6.1 Absolute Maximum Ratings         |   | 10.1 Transient Protection                            | 27                |

| 6.2 ESD Ratings                      |   | 10.2 TVS Selection for 12-V Battery Systems          | 28                |

| 6.3 Recommended Operating Conditions |   | 10.3 TVS Selection for 24-V Battery Systems          | 28                |

| 6.4 Thermal Information              |   | 11 Layout                                            | 29                |

| 6.5 Electrical Characteristics       |   | 11.1 Layout Guidelines                               | <mark>2</mark> 9  |

| 6.6 Switching Characteristics        |   | 11.2 Layout Example                                  | 29                |

| 6.7 Typical Characteristics          |   | 12 Device and Documentation Support                  | 30                |

| 7 Parameter Measurement Information  |   | 12.1 Receiving Notification of Documentation Updates | s <mark>30</mark> |

| 8 Detailed Description               |   | 12.2 Support Resources                               | 30                |

| 8.1 Overview                         |   | 12.3 Trademarks                                      | 30                |

| 8.2 Functional Block Diagram         |   | 12.4 Electrostatic Discharge Caution                 | 30                |

| 8.3 Feature Description              |   | 12.5 Glossary                                        | 30                |

| 8.4 Device Functional Modes          |   | 13 Mechanical, Packaging, and Orderable              |                   |

| 8.5 Application Examples             |   | Information                                          | 30                |

| *** · 4-1                            |   |                                                      |                   |

4 Revision History 注:以前版本的页码可能与当前版本的页码不同

| С | hanges from Revisior | * (May 2020) to Revision A (December 2020) | Page |

|---|----------------------|--------------------------------------------|------|

| • | 更新了整个文档的表、           | 图和交叉参考的编号格式                                | 1    |

| • | 将状态从"预告信息"           | 更改为"量产数据"                                  | 1    |

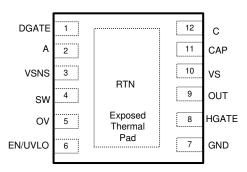

# **5 Pin Configuration and Functions**

图 5-1. 12-Pin WSON Top View

表 5-1. Pin Functions

|         | PIN         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|---------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         | LM74810-Q1  | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| NAME    | WSON        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| DGATE   | 1           | 0    | Diode Controller Gate Drive Output. Connect to the GATE of the external MOSFET. Anode of the ideal diode.                                                                                                                                                                                                                                                                                                                                     |  |

| Α       | 2           | ı    | Anode of the ideal diode. Connect to the source of the external MOSFET                                                                                                                                                                                                                                                                                                                                                                        |  |

| VSNS    | 3           | I    | Voltage sensing input.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| SW      | 4           | ı    | Voltage sensing disconnect switch terminal. VSNS and SW are internally connected through a switch. Use SW as the top connection of the battery sensing or OV resistor ladder network. When EN/UVLO is pulled low, the swit is OFF disconnecting the resistor ladder from the battery line thereby cutting the leakage current. If the internal disconnect switch between VSNS and SW not used then short them together and connect to VS pin. |  |

| OV      | 5           | I    | Adjustable over voltage threshold input. Connect a resistor ladder across SW to OV terminal. When the voltage at OVP exceeds the over voltage cut-off threshold then the HGATE is pulled low turning OFF the HSFET. HGATE turns ON when the sense voltage goes below the OVP falling threshold.                                                                                                                                               |  |

| EN/UVLO | 6           | I    | EN/UVLO Input. Connect to VS pin for always ON operation. Can be driven externally from a mirco controller I/O. Pulling it low below V <sub>(ENF)</sub> makes the device enter into low Iq shutdown mode. For UVLO, connect an external resistor ladder to EN/UVLO to GND.                                                                                                                                                                    |  |

| GND     | 7           | G    | Connect to the system ground plane.                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| HGATE   | 8           | 0    | GATE driver output for the HSFET. Connect to the GATE of the external FET                                                                                                                                                                                                                                                                                                                                                                     |  |

| OUT     | 9           | I    | Connect to the output rail (external MOSFET source).                                                                                                                                                                                                                                                                                                                                                                                          |  |

| vs      | 10          | 1    | Input power supply to the IC. Connect VS to middle point of the common drain back to back MOSFET configuration. Connect a 100nF capacitor across VS a GND pins.                                                                                                                                                                                                                                                                               |  |

| CAP     | 11          | 0    | Charge pump output. Connect a 100-nF capacitor across CAP and VS pins.                                                                                                                                                                                                                                                                                                                                                                        |  |

| С       | 12          | ı    | Cathode of the ideal diode. Connect to the drain of the external MOSFET                                                                                                                                                                                                                                                                                                                                                                       |  |

| RTN     | Thermal Pad | _    | Leave exposed pad floating. Do not connect to GND plane.                                                                                                                                                                                                                                                                                                                                                                                      |  |

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                                       |                                                                           | MIN              | MAX                | UNIT |

|---------------------------------------|---------------------------------------------------------------------------|------------------|--------------------|------|

|                                       | A to GND                                                                  | - 65             | 70                 |      |

|                                       | VS to GND                                                                 | - 1              | 70                 |      |

|                                       | VSNS, SW, EN/UVLO, C, OV, OUT to GND, V <sub>(A)</sub> > 0 V              | - 0.3            | 70                 | V    |

| Input Pins                            | VSNS, SW, EN/UVLO, C, OV, OUT to GND, $V_{(A)} \leqslant 0 \text{ V}$     | V <sub>(A)</sub> | $(70 + V_{(A)})$   |      |

| Input Fins                            | RTN to GND                                                                | - 65             | 0.3                |      |

|                                       | I <sub>VSNS</sub> , I <sub>SW</sub>                                       | - 1              | 10                 | mA   |

|                                       | $I_{EN/UVLO}$ , $I_{OV}$ , $V_{(A)} > 0 V$                                | - 1              |                    | mA   |

|                                       | $I_{\text{EN/UVLO}}, I_{\text{OV}, V_{\text{(A)}}} \leqslant 0 \text{ V}$ | Internally I     | Internally limited |      |

| Output Pins                           | OUT to VS                                                                 | - 65             | 16.5               | V    |

|                                       | CAP to VS                                                                 | - 0.3            | 15                 |      |

| Output Pins                           | CAP to A                                                                  | - 0.3            | 85                 |      |

| Output Pins                           | DGATE to A                                                                | - 0.3            | 15                 | V    |

|                                       | HGATE to OUT                                                              | - 0.3            | 15                 |      |

| Output to Input Pins                  | C to A                                                                    | - 5              | 85                 |      |

| Operating junction temperat           | perating junction temperature, T <sub>j</sub> <sup>(2)</sup>              |                  | 150                | °C   |

| Storage temperature, T <sub>stg</sub> |                                                                           | - 40             | 150                |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                         |                                | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|--------------------------------|-------|------|

|                    | Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> |                                | ±2000 |      |

| V <sub>(ESD)</sub> |                         | Charged device model (CDM), per AEC Q100-011            | Corner pins (DGATE, OV, and C) | ±750  | v    |

|                    |                         |                                                         | Other pins                     | ±500  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)(1)

|                                         |                               | MIN  | NOM MAX | UNIT |

|-----------------------------------------|-------------------------------|------|---------|------|

|                                         | A to GND                      | - 60 | 65      | V    |

| Input Pins                              | VS to GND                     | 0    | 65      | V    |

|                                         | EN/UVLO to GND                | 0    | 65      | V    |

| External<br>Capacitanc<br>e             | CAP to A, VS to GND, A to GND | 0.1  |         | μF   |

| External<br>MOSFET<br>max VGS<br>rating | DGATE to A and HGATE to OUT   | 15   |         | V    |

Product Folder Links: LM7481-Q1

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

# **6.3 Recommended Operating Conditions (continued)**

over operating free-air temperature range (unless otherwise noted)(1)

|    |                                               | MIN  | NOM MAX | UNIT |

|----|-----------------------------------------------|------|---------|------|

| Tj | Operating Junction temperature <sup>(2)</sup> | - 40 | 150     | °C   |

<sup>(1)</sup> Recommended Operating Conditions are conditions under which the device is intended to be functional. For specifications and test conditions, see Electrical Characteristics.

#### 6.4 Thermal Information

|                        |                                              | LM74810-Q1 |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC(1)                            | DRR (WSON) | UNIT |

|                        |                                              | 12 PINS    |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 60.9       | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 48         | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 31.5       | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 1.2        | °C/W |

| $\Psi_{JB}$            | Junction-to-board characterization parameter | 31.4       | °C/W |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 7.1        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **6.5 Electrical Characteristics**

$T_J$  =  $-40^{\circ}$ C to +125 $^{\circ}$ C; typical values at  $T_J$  = 25 $^{\circ}$ C,  $V_{(A)}$  =  $V_{(OUT)}$  =  $V_{(VS)}$  =  $V_{(VSNS)}$  = 12 V,  $V_{(AC)}$  = 20 mV,  $V_{(VCAP)}$  = 0.1  $\mu$ F,  $V_{(EN/UVLO)}$  = 2 V, over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                                     | TEST CONDITIONS                                                            | MIN   | TYP   | MAX   | UNIT |

|------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------|-------|-------|-------|------|

| SUPPLY VOL             | TAGE                                                          |                                                                            |       |       |       |      |

| V <sub>(VS)</sub>      | Operating input voltage                                       |                                                                            | 3     |       | 65    | V    |

| V <sub>(VS_PORR)</sub> | VS POR threshold, rising                                      |                                                                            | 2.4   | 2.6   | 2.85  | V    |

| V <sub>(VS_PORF)</sub> | VS POR threshold, falling                                     |                                                                            | 1.9   | 2.1   | 2.3   | V    |

| I <sub>(SHDN)</sub>    | SHDN current, I <sub>(GND)</sub>                              | V <sub>(EN/UVLO)</sub> = 0 V                                               |       | 2.87  | 5     | μΑ   |

| 1                      | Total System Quiescent current, I <sub>(GND)</sub>            | V <sub>(EN/UVLO)</sub> = 2 V                                               |       | 396   |       | μA   |

| $I_{(Q)}$              | Total System Quiescent current, I(GND)                        | V <sub>(A)</sub> = V <sub>(VS)</sub> = 24 V, V <sub>(EN/UVLO)</sub> = 2 V  |       | 408   | 480   | μA   |

| 1                      | I <sub>(A)</sub> leakage current during Reverse Polarity,     |                                                                            |       | 19    | 112   | μA   |

| I <sub>(REV)</sub>     | I <sub>(OUT)</sub> leakage current during Reverse<br>Polarity | $0 \text{ V} \leqslant \text{V}_{(A)} \leqslant -65 \text{ V}$             |       |       | 1     | μA   |

| ENABLE AND             | UNDERVOLTAGE LOCKOUT (EN/UVLO) I                              | NPUT                                                                       |       |       | '     |      |

| V <sub>(UVLOR)</sub>   | EN/UVLO threshold voltage, rising                             |                                                                            | 1.195 | 1.231 | 1.267 | V    |

| V <sub>(UVLOF)</sub>   | EN/UVLO threshold voltage, falling                            |                                                                            | 1.091 | 1.132 | 1.159 | V    |

| $V_{(ENF)}$            | Enable threshold voltage for low Iq shutdown, falling         |                                                                            | 0.3   | 0.67  | 0.93  | V    |

| V <sub>(EN_Hys)</sub>  | Enable Hysteresis                                             |                                                                            | 37    | 72    | 95    | mV   |

| I <sub>(EN/UVLO)</sub> |                                                               | $0 \text{ V} \leqslant \text{V}_{(\text{EN/UVLO})} \leqslant 65 \text{ V}$ |       | 52    | 200   | nA   |

| OVER VOLTA             | GE PROTECTION AND BATTERY SENSING                             | G (VSNS, SW, OV) INPUT                                                     |       |       |       |      |

| R <sub>(SW)</sub>      | Battery sensing disconnect switch resistance                  | $3 \text{ V} \leqslant \text{V}_{(SNS)} \leqslant 65 \text{ V}$            | 10    | 19.5  | 46    | Ω    |

| V <sub>(OVR)</sub>     | Overvoltage threshold input, rising                           |                                                                            | 1.195 | 1.231 | 1.267 | V    |

| V <sub>(OVF)</sub>     | Overvoltage threshold input, falling                          |                                                                            | 1.091 | 1.13  | 1.159 | V    |

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

# 6.5 Electrical Characteristics (continued)

$T_J$  =  $-40^{\circ}$ C to +125 $^{\circ}$ C; typical values at  $T_J$  = 25 $^{\circ}$ C,  $V_{(A)}$  =  $V_{(OUT)}$  =  $V_{(VS)}$  =  $V_{(VS)}$  = 12 V,  $V_{(AC)}$  = 20 mV,  $V_{(VCAP)}$  = 0.1  $\mu$ F,  $V_{(EN/UVLO)}$  = 2 V, over operating free-air temperature range (unless otherwise noted)

|                                           | PARAMETER                                                                                     | TEST CONDITIONS                                                                         | MIN   | TYP  | MAX   | UNIT |

|-------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|------|-------|------|

| I <sub>(OV)</sub>                         | OV Input leakage current                                                                      | 0 V ≤ V <sub>(OV)</sub> ≤ 65 V                                                          |       | 53   | 200   | nA   |

| CHARGE PUMP (                             | CAP)                                                                                          |                                                                                         |       |      |       |      |

| I <sub>(CAP)</sub>                        | Charge Pump source current (Charge pump on)                                                   | $V_{(CAP)} - V_{(A)} = 7 \text{ V, } 6 \text{ V} \leqslant V_{(S)} \leqslant 65$        | 2.5   | 3.8  |       | mA   |

| VCAP - VS                                 | Charge Pump Turn ON voltage                                                                   |                                                                                         | 11    | 12.2 | 13.2  | V    |

| VCAP - VS                                 | Charge Pump Turnoff voltage                                                                   |                                                                                         | 11.9  | 13.2 | 14.1  | V    |

| V                                         | Charge Pump UVLO voltage threshold, rising                                                    |                                                                                         | 5.4   | 6.6  | 7.9   | V    |

| V <sub>(CAP UVLO)</sub>                   | Charge Pump UVLO voltage threshold, falling                                                   |                                                                                         | 4.4   | 5.5  | 6.6   | V    |

| IDEAL DIODE (A,                           | C, DGATE)                                                                                     |                                                                                         |       |      | '     |      |

| V <sub>(A_PORR)</sub>                     | V <sub>(A)</sub> POR threshold, rising                                                        |                                                                                         | 2.2   | 2.35 | 2.6   | V    |

| V <sub>(A_PORF)</sub>                     | V <sub>(A)</sub> POR threshold, falling                                                       |                                                                                         | 2     | 2.2  | 2.4   | V    |

| $V_{(AC\_REG)}$                           | Regulated Forward V <sub>(A)</sub> - V <sub>(C)</sub><br>Threshold                            |                                                                                         | 5.8   | 9.1  | 12.4  | mV   |

| V <sub>(AC_REV)</sub>                     | V <sub>(A)</sub> <sup>-</sup> V <sub>(C)</sub> Threshold for Fast Reverse<br>Current Blocking |                                                                                         | - 6.4 | - 4  | - 1.3 | mV   |

| V <sub>(AC_FWD)</sub>                     | V <sub>(A)</sub> - V <sub>(C)</sub> Threshold for Reverse to Forward transition               |                                                                                         | 150   | 177  | 200   | mV   |

|                                           | Gate Drive Voltage                                                                            | 3 V < V <sub>(S)</sub> < 5 V                                                            | 7     |      |       | V    |

| $V_{(DGATE)} - V_{(A)}$                   | Gate Drive voltage                                                                            | 5 V < V <sub>(S)</sub> < 65 V                                                           | 10    | 11.5 | 13    | V    |

|                                           | Peak Gate Source current                                                                      | $V_{(A)} - V_{(C)} = 100 \text{ mV}, V_{(DGATE)} - V_{(A)}$                             |       | 60   |       | mA   |

| I <sub>(DGATE)</sub>                      | Peak Gate Sink current                                                                        | $V_{(A)} - V_{(C)} = -12 \text{ mV}, V_{(DGATE)} - V_{(A)} = 11 \text{ V}$              |       | 2670 |       | mA   |

|                                           | Regulation sink current                                                                       | V <sub>(A)</sub> - V <sub>(C)</sub> = 0 V, V <sub>(DGATE)</sub> - V <sub>(A)</sub> = 11 | 8.4   | 14.9 |       | μA   |

| I <sub>(C)</sub>                          | Cathode leakage Current                                                                       | V <sub>(A)</sub> = -14 V, V <sub>(C)</sub> = 12 V                                       | 4     | 9    | 32    | μA   |

| HIGH SIDE CONTI                           | ROLLER (HGATE, OUT, SNS, SW, OV)                                                              |                                                                                         |       |      |       |      |

| V - V                                     | Gate Drive Voltage                                                                            | 3 V < V <sub>(S)</sub> < 5 V                                                            | 7     |      |       | V    |

| V <sub>(HGATE)</sub> - V <sub>(OUT)</sub> | Gate Drive voltage                                                                            | 5 V < V <sub>(S)</sub> < 65 V                                                           | 10    | 11.1 | 14.5  | V    |

| I                                         | Source Current                                                                                |                                                                                         | 39    | 55   | 75    | μΑ   |

| I(HGATE)                                  | Sink Current                                                                                  | $V_{(OV)} > V_{(OVR)}$                                                                  | 168   | 260  |       | mA   |

|                                           |                                                                                               |                                                                                         |       |      |       |      |

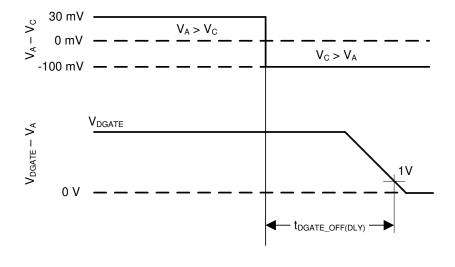

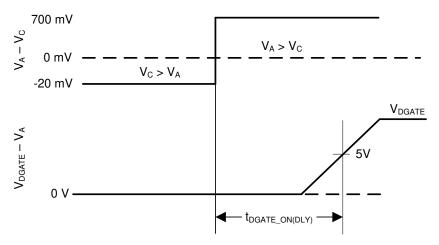

# **6.6 Switching Characteristics**

$T_J$  =  $-40^{\circ}$ C to +125°C; typical values at  $T_J$  = 25°C,  $V_{(A)}$  =  $V_{(C)}$  =  $V_{(OUT)}$  =  $V_{(VS)}$  = 12V,  $V_{(AC)}$  = 20 mV,  $C_{(VCAP)}$  = 0.1  $\mu$ F,  $V_{(EN/UVLO)}$  = 2 V, over operating free-air temperature range (unless otherwise noted)

|                             | PARAMETER                                            | TEST CONDITIONS                                                                                                      | MIN | TYP  | MAX   | UNIT |

|-----------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|------|-------|------|

| t <sub>DGATE_OFF(dly)</sub> | DGATE Turnoff Delay during reverse voltage detection | $V_{(A)} - V_{(C)} = +30 \text{ mV to } -100 \text{ mV}$ to $V_{(DGATE - A)} < 1 \text{ V}, C_{(DGATE - A)} = 10$ nF |     | 0.5  | 0.875 | μs   |

| t <sub>DGATE_ON(dly)</sub>  | DGATE Turnon Delay during forward voltage detection  | $V_{(A)} - V_{(C)} = -20$ mV to +700 mV to $V_{(DGATE-A)} > 5$ V, $C_{(DGATE-A)} = 10$ nF                            |     | 0.85 | 1.6   | μs   |

| t <sub>EN(dly)_DGATE</sub>  | DGATE Turnon Delay during EN/<br>UVLO                | EN/UVLO $\uparrow$ to V <sub>(DGATE-A)</sub> > 5V,<br>C <sub>(DGATE-A)</sub> = 10 nF                                 | 98  | 175  | 270   | μs   |

Product Folder Links: LM7481-Q1

# **6.6 Switching Characteristics (continued)**

$T_J$  =  $-40^{\circ}$ C to +125°C; typical values at  $T_J$  = 25°C,  $V_{(A)}$  =  $V_{(C)}$  =  $V_{(OUT)}$  =  $V_{(VS)}$  = 12V,  $V_{(AC)}$  = 20 mV,  $C_{(VCAP)}$  = 0.1  $\mu$ F,  $V_{(EN/UVLO)}$  = 2 V, over operating free-air temperature range (unless otherwise noted)

|                                 | PARAMETER                                 | TEST CONDITIONS      | MIN | TYP  | MAX | UNIT |

|---------------------------------|-------------------------------------------|----------------------|-----|------|-----|------|

| t <sub>EN_OFF(deg)_DGATE</sub>  | DGATE Turnoff Deglitch during EN/<br>UVLO | EN/UVLO ↓ to DGATE ↓ |     | 8.1  |     | μs   |

| t <sub>EN_OFF(deg)_HGATE</sub>  | HGATE Turnoff Deglitch during EN/<br>UVLO | EN/UVLO ↓ to HGATE ↓ | 3   | 4.6  | 6   | μs   |

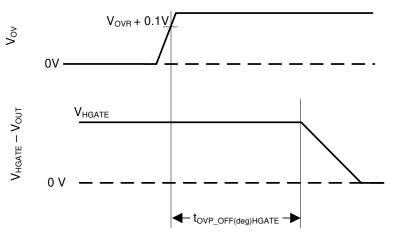

| t <sub>OVP_OFF(deg)_HGAT</sub>  | HGATE Turnoff Deglitch during OV          | OV ↑ to HGATE ↓      |     | 3.98 | 5.4 | μs   |

| t <sub>OVP_ON(deg)_</sub> HGATE | HGATE Turnon Deglitch during OV           | OV ↓ to HGATE ↑      |     | 2.95 |     | μs   |

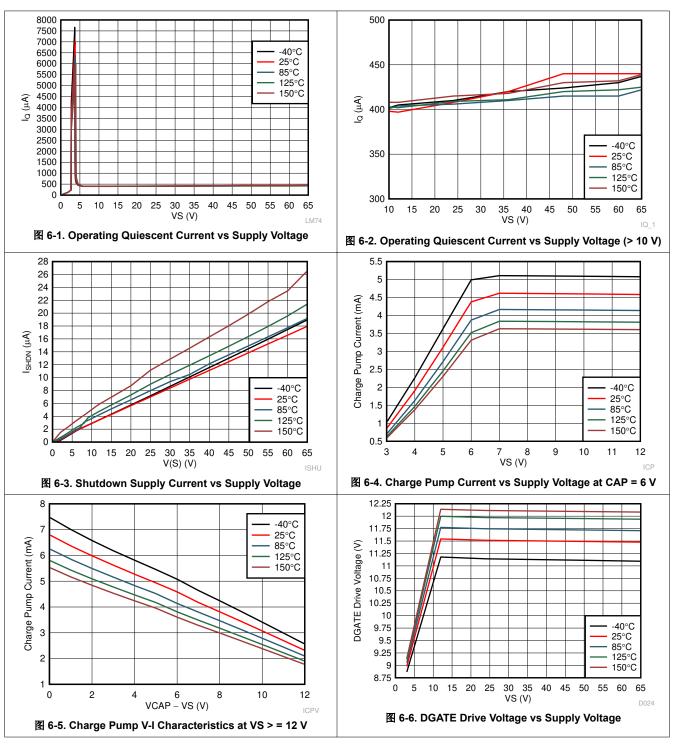

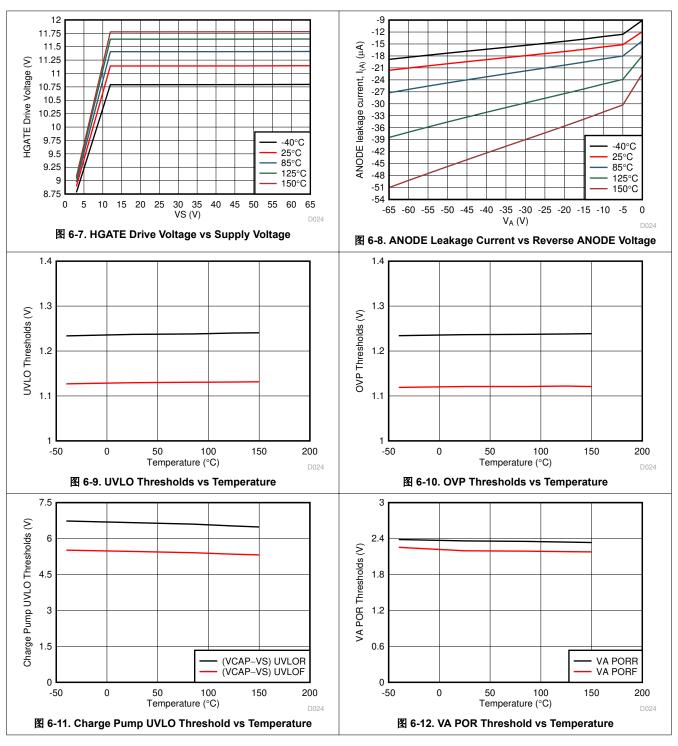

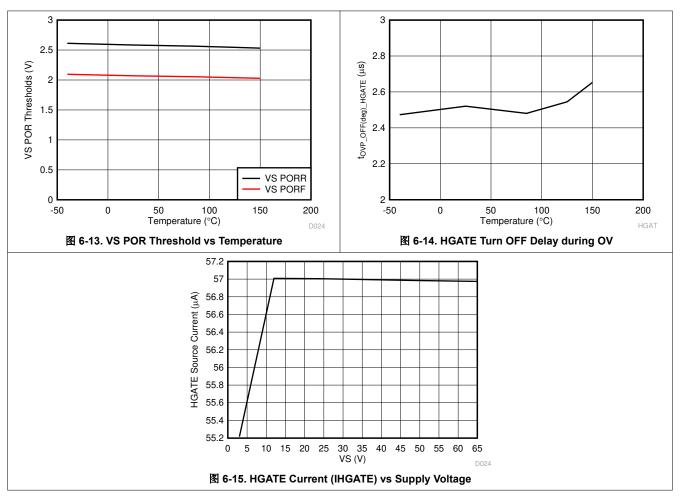

# 6.7 Typical Characteristics

# **6.7 Typical Characteristics (continued)**

# **6.7 Typical Characteristics (continued)**

# 7 Parameter Measurement Information

图 7-1. Timing Waveforms

# 8 Detailed Description

#### 8.1 Overview

The LM74810-Q1 ideal diode controller drives and controls external back to back N-Channel MOSFETs to emulate an ideal diode rectifier with power path ON/OFF control, inrush current limiting and over voltage protection. The wide input supply of 3 V to 65 V allows protection and control of 12-V and 24-V automotive battery powered ECUs. The device can withstand and protect the loads from negative supply voltages down to - 65 V. An integrated ideal diode controller (DGATE) drives the first MOSFET to replace a Schottky diode for reverse input protection and output voltage holdup. A strong charge pump with 60-mA peak GATE source current driver stage and short turn ON and turn OFF delay times ensures fast transient response ensuring robust performance during automotive testing such as ISO16750 or LV124 where an ECU is subjected to AC superimpose input signals upto 200-KHz frequency. With a second MOSFET in the power path the device allows load disconnect (ON/OFF control) and over voltage protection using HGATE control. The device features an adjustable over voltage cut-off protection feature using a programming resistor across SW and OVP terminal.

The LM74810-Q1 controls the DGATE of the MOSFET to regulate the forward voltage drop at 9.1 mV. The linear regulation scheme in these devices enables graceful control of the GATE voltage and turns off of the MOSFET during a reverse current event and ensures zero DC reverse current flow.

The device features enable control. With the enable pin low during the standby mode, both the external MOSFETs and controller is off and draws a very low 2.87 μ A of current. The high voltage rating of LM74810-Q1 helps to simplify the system designs for automotive ISO7637 protection. The LM74810-Q1 are also suitable for ORing applications

### 8.2 Functional Block Diagram

Product Folder Links: 1 M7481-Q1

# 8.3 Feature Description

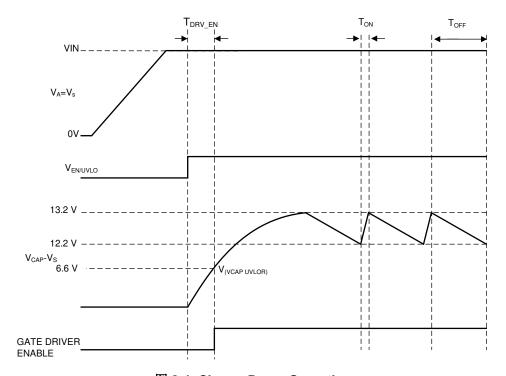

#### 8.3.1 Charge Pump

The charge pump supplies the voltage necessary to drive the external N-channel MOSFET. An external charge pump capacitor is placed between CAP and VS pins to provide energy to turn on the external MOSFET. In order for the charge pump to supply current to the external capacitor the EN/UVLO pin voltage must be above the specified input high threshold,  $V_{(ENR)}$ . When enabled, the charge pump sources a charging current of 3.8-mA typical. If EN/UVLO pin is pulled low, then the charge pump remains disabled. To ensure that the external MOSFET can be driven above its specified threshold voltage, the CAP to VS voltage must be above the undervoltage lockout threshold, typically 6.6 V, before the internal gate driver is enabled. Use 1 to calculate the initial gate driver enable delay.

$$T_{\left(\mathsf{DRV\_EN}\right)} = 175 \mu s + C_{\left(\mathsf{CAP}\right)} x \frac{V_{\left(\mathsf{CAP\_UVLOR}\right)}}{3.8 m A} \tag{1}$$

#### where

- C<sub>(CAP)</sub> is the charge pump capacitance connected across VS and CAP pins

- V<sub>(CAP UVLOR)</sub> = 6.6 V (typical)

To remove any chatter on the gate drive approximately 1 V of hysteresis is added to the VCAP undervoltage lockout. The charge pump remains enabled until the CAP to VS voltage reaches 13.2 V, typically, at which point the charge pump is disabled decreasing the current draw on the VS pin. The charge pump remains disabled until the CAP to VS voltage is below to 12.2 V typically at which point the charge pump is enabled. The voltage between CAP and VS continue to charge and discharge between 12.2 V and 13.2 V as shown in  $\boxtimes$  8-1. By enabling and disabling the charge pump, the operating quiescent current of the LM74810-Q1 is reduced. When the charge pump is disabled it sinks 15  $\mu$ A.

图 8-1. Charge Pump Operation

#### 8.3.2 Dual Gate Control (DGATE, HGATE)

The LM74810-Q1 features two separate gate control and driver outputs to drive back to back N-channel MOSFETs.

#### 8.3.2.1 Reverse Battery Protection (A, C, DGATE)

A, C, DGATE comprises of Ideal Diode stage. Connect the Source of the external MOSFET to A, Drain to C and Gate to DGATE. The LM74810-Q1 has integrated reverse input protection down to -65 V.

Before the DGATE driver is enabled, following conditions must be achieved:

- The EN/UVLO pin voltage must be greater than the specified input high voltage.

- The CAP to VS voltage must be greater than the undervoltage lockout voltage.

- Voltage at A pin must be greater than VA POR Rising threshold.

- Voltage at Vs pin must be greater than Vs POR Rising thershold.

If the above conditions are not achieved, then the DGATE pin is internally connected to the A pin, assuring that the external MOSFET is disabled.

In LM74810-Q1 the voltage drop across the MOSFET is continuously monitored between the A and C pins, and the DGATE to A voltage is adjusted as needed to regulate the forward voltage drop at 9.1 mV (typ). This closed loop regulation scheme enables graceful turn off of the MOSFET during a reverse current event and ensures zero DC reverse current flow. This scheme ensures robust performance during slow input voltage ramp down tests. Along with the linear regulation amplifier scheme, the LM74810-Q1 also integrates a fast reverse voltage comparator. When the voltage drop across A and C reaches  $V_{(AC\_REV)}$  threshold then the DGATE goes low within 0.5-µs (typ). This fast reverse voltage comparator scheme ensures robust performance during fast input voltage ramp down tests such as input micro-shorts. The external MOSFET is turned ON back when the voltage across A and C hits  $V_{(AC\_FWD)}$  threshold within 0.85 µs (typ).

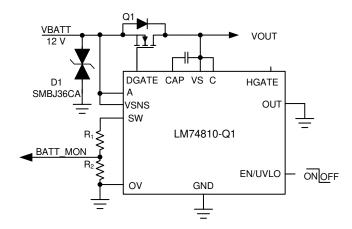

For Ideal Diode only designs, connect LM74810-Q1 as shown in 🛚 8-2.

图 8-2. Configuring LM74810-Q1 for Ideal Diode Only

#### 8.3.2.2 Load Disconnect Switch Control (HGATE, OUT)

HGATE and OUT comprises of Load disconnect switch control stage. Connect the Source of the external MOSFET to OUT and Gate to HGATE.

Before the HGATE driver is enabled, following conditions must be achieved:

- The EN/UVLO pin voltage must be greater than the specified input high voltage.

- The CAP to VS voltage must be greater than the undervoltage lockout voltage.

- Voltage at Vs pin must be greater than Vs POR Rising thershold.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

If the above conditions are not achieved, then the HGATE pin is internally connected to the OUT pin, assuring that the external MOSFET is disabled.

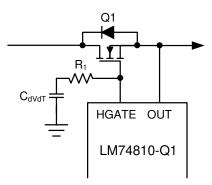

For Inrush Current limiting, connect  $C_{dVdT}$  capacitor and  $R_1$  as shown in 8-3.

图 8-3. Inrush Current Limiting

The  $C_{dVdT}$  capacitor is required for slowing down the HGATE voltage ramp during power up for inrush current limiting. Use 方程式 2 to calculate  $C_{dVdT}$  capacitance value .

$$C_{dVdT} = \frac{I_{HGATE\_DRV}}{I_{INRUSH}} x C_{OUT}$$

(2)

where  $I_{HATE\_DRV}$  is 55  $\mu$  A (typ),  $I_{INRUSH}$  is the inrush current and  $C_{OUT}$  is the output load capacitance. An extra resistor,  $R_1$ , in series with the  $C_{dVdT}$  capacitor improves the turn off time.

For Load disconnect switch only designs, configure the LM74810-Q1 as shown in \ 8-4

图 8-4. Configuring LM74810-Q1 for Load Disconnect Switch Only

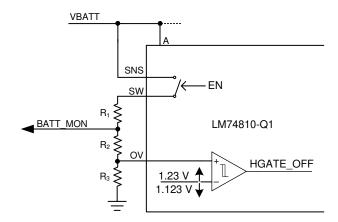

# 8.3.3 Over Voltage Protection and Battery Voltage sensing (VSNS, SW, OV)

Connect a resistor ladder as shown in 8 8-5 for Over Voltage threshold programming.

图 8-5. Programming Over Voltage Threshold and Battery Sensing

A disconnect switch is integrated between VSNS and SW pins. This switch is turned OFF when EN/UVLO pin is pulled low. This helps to reduce the leakage current through the resistor divider network during system shutdown state (IGN\_OFF state).

#### 8.3.4 Low Iq Shutdown and Under Voltage Lockout (EN/UVLO)

The enable pin allows for the gate driver to be either enabled or disabled by an external signal. If the EN/UVLO pin voltage is greater than the rising threshold, the gate driver and charge pump operates as described in Charge Pump section. If EN/UVLO pin voltage is less than the input low threshold, V<sub>(ENF)</sub>, the charge pump and both the gate drivers (DGATE and HGATE) are disabled placing the LM74810-Q1 in shutdown mode.

If  $V_{(ENF)} < V_{(EN/UVLO)} < V_{(UVLOF)}$  then only HGATE is disabled disconnecting the load from the supply, DGATE remains ON.

The EN/UVLO pin can withstand a maximum voltage of 65 V. For always ON operation connect EN/UVLO pin to VS.

#### 8.4 Device Functional Modes

The LM74810-Q1 enters shutdown mode when the EN/UVLO pin voltage is below the specified input low threshold  $V_{(ENF)}$ . Both the gate drivers and the charge pump are disabled in shutdown mode. During shutdown mode the LM74810-Q1 enters low IQ operation with a total input quiescent consumption of 2.87  $\,^{\,\mu}$  A (typ). When the LM74810-Q1 is in shutdown mode, forward current flow to always ON loads connected to the common drain point of the back to back MOSFETs is not interrupted but is conducted through the MOSFET's body diode.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

### 8.5 Application Examples

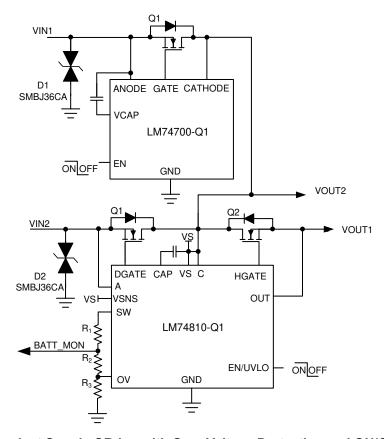

# 8.5.1 Redundant Supply OR-ing with Inrush Current Limiting, Over Voltage Protection and ON/OFF Control

图 8-6. Redundant Supply OR-ing with Over Voltage Protection and ON/OFF Control

8-6 shows the implementation of Dual OR-ing with Inrush Current Limiting, Over Voltage Protection and power path ON/OFF control. The input side SMBJ36CA TVS across the ideal diodes is required for ISO7637 Pulse 1 transient suppression to limit the input voltage within the device max voltage rating of −65 V.

R1 and R2 are the programming resistors for over voltage protection (OVP) threshold. When the voltage at OVP pin exceeds OVP cut-off reference threshold then the HGATE driver turns OFF the FET Q3, disconnecting the power path and protecting the downstream load. HGATE goes high once the OVP pin voltage goes below the OVP falling hysteresis threshold. Use 0.1-  $\mu$  F to 1-  $\mu$  F capacitor across VS to CAP pins of the LM74810-Q1. This is the charge pump capacitor and acts as the supply for both the DGATE and HGATE driver stages. The DGATE driver of the LM74810-Q1 is equipped with 60-mA peak source current and 1.5-A peak sink current capability resulting in fast and efficient transient responses during the ISO16750 or LV124 short interruptions as well as AC superimpose testing.

Pull EN low during the sleep/standby mode. With EN low, both the DGATE and HGATE drivers are pulled low turning OFF both the power FETs. VOUT1 gets disconnected from the VBATT rail reducing the system  $I_Q$ . VOUT2 is gets power through the body diode of the MOSFET Q2 and this supply can be utilized for always ON loads. The LM74810-Q1 draws a 2.87-  $\mu$  A current during this mode.

# 9 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

#### 9.1 Application Information

LM74810-Q1 controls two N-channel power MOSFETs with DGATE used to control diode MOSFET to emulate an ideal diode and HGATE controlling second MOSFET for power path cut-off when disabled or during an over voltage protection. HGATE controlled MOSFET can be used to clamp the output during over voltage or load dump conditions. LM74810-Q1 can be placed into low quiescent current mode using EN/UVLO, where both DGATE and HGATE are turned OFF.

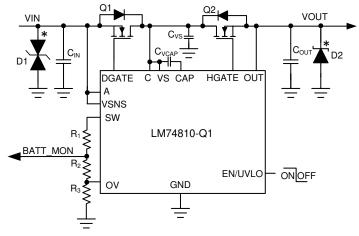

# 9.2 Typical 12-V Reverse Battery Protection Application

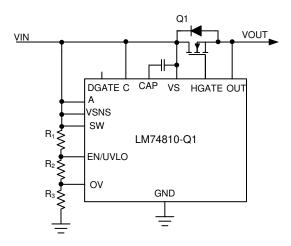

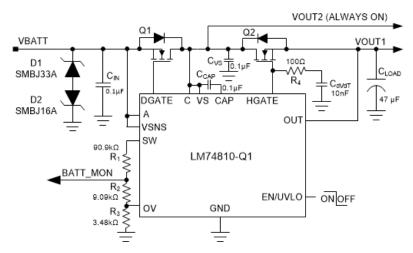

A typical application circuit of LM74810-Q1 configured to provide reverse battery protection with over voltage protection is shown in § 9-1.

图 9-1. Typical Application Circuit - 12-V Reverse Battery Protection and Over Voltage Protection

### 9.2.1 Design Requirements for 12-V Battery Protection

The system design requirements are listed in 表 9-1.

表 9-1. Design Parameters - 12-V Reverse Battery Protection and Over Voltage Protection

| DESIGN PARAMETER                         | EXAMPLE VALUE                                                             |  |  |  |  |

|------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|

| Operating Input Voltage Range            | 12-V battery, 12-V nominal with 3.2-V Cold Crank and 35-V Load  Dump      |  |  |  |  |

| Output Power                             | 200 W                                                                     |  |  |  |  |

| Output Current Range                     | 12-A Nominal, 18-A maximum                                                |  |  |  |  |

| Input Capacitance                        | 0.1-μF minimum                                                            |  |  |  |  |

| Output Capacitance                       | 0.1-μF minimum, (optional 470bμF for E-10 functional class A performance) |  |  |  |  |

| Over Voltage Cut-off                     | 37.0 V, output cut-off >37.0 V                                            |  |  |  |  |

| AC Super Imposed Test                    | 2-V Peak-Peak to 6-V Peak-Peak, 20 Hz to 30 KHz extendable to 200 KHz     |  |  |  |  |

| Automotive Transient Immunity Compliance | ISO 7637-2, ISO 16750-2 and LV124                                         |  |  |  |  |

| Battery Monitor Ratio                    | 8:1                                                                       |  |  |  |  |

Product Folder Links: LM7481-Q1

#### 9.2.2 Automotive Reverse Battery Protection

The LM74810-Q1 feature two separate gate control and driver outputs i.e DGATE and HGATE to drive back to back N-channel MOSFETs. This enables LM74810-Q1 to provide comprehensive immunity with robust system protection during various automotive transient tests as per ISO 7637-2 and ISO 16750-2 standard as well as other automotive OEM standards. For more information, see the *Automotive EMC-compliant reverse-battery protection with ideal-diode controllers* article.

LM74810-Q1 gate drive output DGATE controls MOSFET Q1 to provide reverse battery protection and true reverse current blocking functionality. HGATE controls MOSFET Q2 to turn off the power path during input over voltage condition. Resistor network R1, R2 and R3 connected to OV and SW can be configured for over voltage protection and also for battery monitoring under normal operating conditions as well as reverse battery conditions. TVS D1 and D2 clamps the automotive transient input voltages on the 12-V battery, both positive and negative transients, to voltage levels safe for MOSFET Q1 and LM74810-Q1.

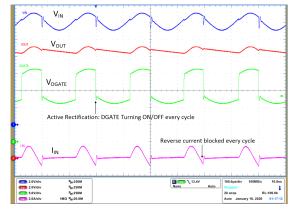

Fast reverse current blocking response and quick reverse recovery enables LM74810-Q1 to turn ON/OFF MOSFET Q1 during AC super imposed input specified by ISO 16750-2 and LV124 E-06 and provide active rectification of the AC input superimposed on DC battery voltage. Fast reverse current blocking response of LM74810-Q1 helps to turn off MOSFET Q1 during negative transients inputs such as - 150-V 2-ms Pulse 1 specified in ISO 7637-2 and input micro short conditions such as LV124 E-10 test.

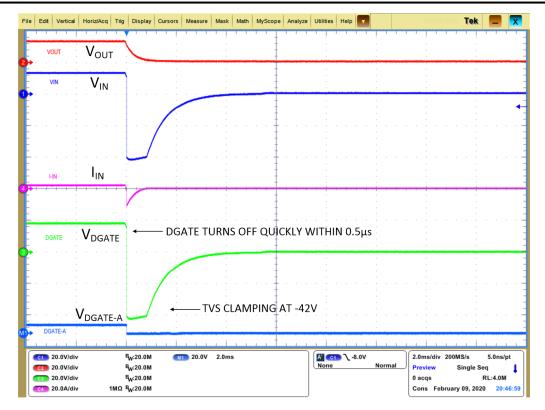

#### 9.2.3 Input Transient Protection: ISO 7637-2 Pulse 1

ISO 7637-2 Pulse 1 specifies negative transient immunity of electronic modules connected in parallel with an inductive load when the battery is disconnected. A typical pulse 1 specified in ISO 7637-2 starts with battery disconnection where supply voltage collapses to 0 V followed by - 150 V 2 ms applied with a source impedance of 10  $\Omega$  at a slew rate of 1  $\mu$ s on the supply input. LM74810-Q1 blocks reverse current and prevents the output voltage from swinging negative, protecting the rest of the electronic circuits from damage due to negative transient voltage. MOSFET Q1 is quickly turned off within 0.5  $\mu$ s by fast reverse comparator of LM74810-Q1.

A single bi-directional TVS or two uni-directional TVS are required at the input to clamp the negative transient pulse within the operating maximum voltage across cathode to anode of 85 V and does not violate the MOSFET Q1 drain-source breakdown voltage rating. ISO 7637-2 Pulse 1 performance of LM74810-Q1 is shown in § 9-2.

Copyright © 2021 Texas Instruments Incorporated

图 9-2. ISO 7637-2 Pulse 1

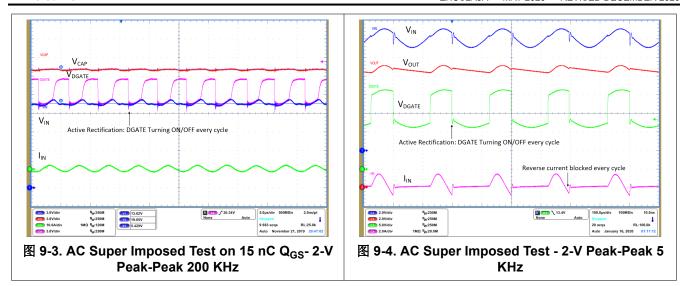

#### 9.2.4 AC Super Imposed Input Rectification: ISO 16750-2 and LV124 E-06

Alternators are used to power the automotive electrical system and charge the battery during normal runtime of the vehicle. Rectified alternator output contains residual AC ripple voltage superimposed on the DC battery voltage due to various reasons which includes engine speed variation, regulator duty cycle with field switching ON/OFF and electrical load variations. On a 12-V battery supply, alternator output voltage is regulated by a voltage regulator between 14.5 V to 12.5 V by controlling the field current of alternator's rotor. All electronic modules are tested for proper operation with superimposed AC ripple on the DC battery voltage. AC super imposed test specified in ISO 16750-2 and LV124 E-06 requires AC ripple of 2-V Peak-Peak on a 13.5-V DC battery voltage, swept from 15 Hz to 30 KHz and extended to 200 KHz in case of LV148 E48-05. LM74810-Q1 rectifies the AC superimposed voltage by turning the MOSFET Q1 OFF quickly to cut-off reverse current and turning the MOSFET Q1 ON quickly during forward conduction.

Active rectification of 2-V peak-peak 200 KHz AC input by LM74810-Q1 is shown in 89-3. Fast turn off and quick turn ON of the MOSFET reduces power dissipation in the MOSFET Q1 and active rectification reduces power dissipation in the output hold-up capacitor's ESR by half. Active rectification of 2-V peak-peak 5-KHz AC input is shown in 89-4.

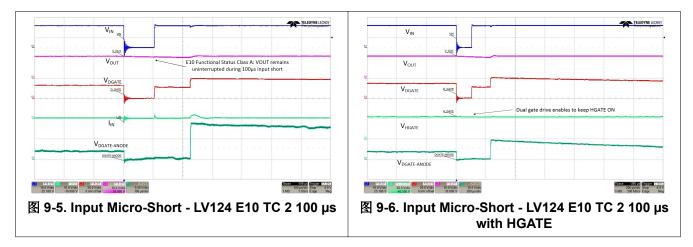

#### 9.2.5 Input Micro-Short Protection: LV124 E-10

E-10 test specified in LV124 standard checks for immunity of electronic modules to short interruptions in power supply input due to contact issues or relay bounce. During this test (case 2), micro-short is applied on the input for a duration as low as 10  $\mu$ s to several ms. For a functional pass status A, electronic modules are required to run uninterrupted during the E-10 test (case 2) with 100- $\mu$ s duration. Dual-Gate drive architecture of LM74810-Q1 - DGATE and HGATE - enables to achieve a functional pass status A with optimum hold up capacitance on the output when compared to a single gate drive controller. When input micro-short is applied for 100  $\mu$ s, LM74810-Q1 quickly turns off MOSFET Q1 by shorting DGATE to ANODE (source of MOSFET) within 0.5  $\mu$ s to prevent the output from discharging and the HGATE remains ON keeping MOSFET Q2 ON, enabling fast recovery after the input short is removed.

Performance of LM74810-Q1 during E10 input power supply interruption test case 2 is shown in  $\boxtimes$  9-5. After the input short is removed, input voltage recovers and MOSFET Q1 is turned back ON within 130  $\mu$ s. Note that dualgate drive topology allows MOSFET Q2 to remain ON during the test and helps in restoring the input power faster. Output voltage remains unperturbed during the entire duration, achieving functional status A.

#### 9.2.6 Detailed Design Procedure

#### 9.2.6.1 Design Considerations

表 9-1 summarizes the design parameters that must be known for designing an automotive reverse battery protection circuit with over voltage cut-off. During power up, inrush current through MOSFET Q2 needs to be limited so that the MOSFET operates well within its SOA. Maximum load current, maximum ambient temperature

and thermal properties of the PCB determine the  $R_{DSON}$  of the MOSFET Q2 and maximum operating voltage determines the voltage rating of the MOSFET Q2. Selection of MOSFET Q2 is determined mainly by the maximum operating load current, maximum ambient temperature, maximum frequency of AC super imposed voltage ripple and ISO 7637-2 pulse 1 requirements. Over voltage threshold is decided based on the rating of downstream DC/DC converter or other components after the reverse battery protection circuit. A single bidirectional TVS or two back-back uni-directional TVS are required to clamp input transients to a safe operating level for the MOSFETs Q1, Q2 and LM74810-Q1.

#### 9.2.6.2 Charge Pump Capacitance VCAP

Minimum required capacitance for charge pump VCAP is based on input capacitance of the MOSFET Q1,  $C_{ISS(MOSFET\_Q1)}$  and input capacitance of Q2  $C_{ISS(MOSFET)}$ .

Charge Pump VCAP: Minimum 0.1  $\mu$ F is required; recommended value of VCAP ( $\mu$ F)  $\geqslant$  10 x (  $C_{ISS(MOSFET\_Q1)} + C_{ISS(MOSFET\_Q2)}$ ) ( $\mu$ F).

#### 9.2.6.3 Input and Output Capacitance

A minimum input capacitance C<sub>IN</sub> of 0.1 μF and output capacitance C<sub>OUT</sub> of 0.1 μF is recommended.

#### 9.2.6.4 Hold-up Capacitance

Usually bulk capacitors are placed on the output due to various reasons such as uninterrupted operation during power interruption or micro-short at the input, hold-up requirements for doing a memory dump before turning of the module and filtering requirements as well. This design considers minimum bulk capacitors requirements for meeting functional status "A" during LV124 E10 test case 2 100-µs input interruption. To achieve functional pass status A, acceptable voltage droop in the output of LM74810-Q1 is based on the UVLO settings of downstream DC-DC converters. For this design, 4.0-V drop in output voltage for 100 µs is considered and the minimum hold-up capacitance required is calculated by

$$C_{HOLD\_UP\_MIN} = \frac{I_{LOAD\_MAX}}{dV_{OUT}} x 100 \,\mu s \tag{3}$$

Minimum hold-up capacitance required to hold output with 4.0-V drop at 18-A current for 100  $\mu$ s is 450  $\mu$ F. A 470-uF electrolytic capacitor is a closest standard value that can be placed at the output. Note that the typical application circuit shows the hold-up capacitor as optional because not all designs require hold-up capacitance.

#### 9.2.6.5 Over Voltage Protection and Battery Monitor

Resistors  $R_1$ ,  $R_2$  and  $R_3$  connected in series are used to program the over voltage threshold and battery monitor ratio. The resistor values required for setting the over voltage threshold  $V_{OV}$  to 37.0 V and battery monitor ratio  $V_{BATT\_MON}$ :  $V_{BATT}$  to 1:8 are calculated by solving 5 and 5 and 5 and 5 are calculated by solving 5 and 5 are 5.

$$V_{OVR} = \frac{R_3}{R_1 + R_2 + R_3} x V_{OV} \tag{4}$$

$$V_{BAT\_MON} = \frac{R_2 + R_3}{R_1 + R_2 + R_3} x V_{BATT}$$

(5)

For minimizing the input current drawn from the battery through resistors  $R_1$ ,  $R_2$  and  $R_3$ , it recommended to use higher value of resistance. Using high value resistors will add error in the calculations because the current through the resistors at higher value will become comparable to the leakage current into the OV pin. Maximum leakage current into the OV pin is 1  $\mu$ A and choosing ( $R_1 + R_2 + R_3$ ) < 120 k $\Omega$  ensures current through resistors is 100 times greater than leakage through OV pin.

Product Folder Links: LM7481-Q1

Based on the device electrical characteristics, V<sub>OVR</sub> is 1.23 V and battery monitor ratio (V<sub>BATT</sub> MON / V<sub>BATT</sub>) is designed for a ratio of 1/8. To limit  $(R_1 + R_2 + R_3)$  < 120 k  $\Omega$ , select  $(R_1 + R_2)$  = 100 k  $\Omega$ . Solving 方程式 4 gives  $R_3$  = 3.45 k  $\Omega$ . Solving 方程式 5 for R2 using ( $R_1$  +  $R_2$ ) = 100 k  $\Omega$  and  $R_3$  = 3.45 k  $\Omega$ , gives  $R_2$  = 9.48 k  $\Omega$  and  $R_1$ = 90.52 k  $\Omega$ .

Standard 1% resistor values closest to the calculated resistor values are R1 = 90.9 k $\Omega$ , R2 = 9.09 k $\Omega$  and R3 =  $3.48 k \Omega$ .

#### 9.2.7 MOSFET Selection: Blocking MOSFET Q1

For selecting the blocking MOSFET Q1, important electrical parameters are the maximum continuous drain current  $I_D$ , the maximum drain-to-source voltage  $V_{DS(MAX)}$ , the maximum drain-to-source voltage  $V_{GS(MAX)}$ , the maximum source current through body diode and the drain-to-source ON resistance R<sub>DSON</sub>.

The maximum continuous drain current, I<sub>D</sub>, rating must exceed the maximum continuous load current.

The maximum drain-to-source voltage, V<sub>DS(MAX)</sub>, must be high enough to withstand the highest differential voltage seen in the application. This would include all the automotive transient events and any anticipated fault conditions. It is recommended to use MOSFETs with  $V_{DS}$  voltage rating of 60 V along with a single bidirectional TVS or a V<sub>DS</sub> rating 40-V maximum rating along with two unidirectional TVS connected back-back at the input.

The maximum V<sub>GS</sub> LM74810-Q1 can drive is 14 V, so a MOSFET with 15-V minimum V<sub>GS</sub> rating should be selected. If a MOSFET with < 15-V V<sub>GS</sub> rating is selected, a zener diode can be used to clamp V<sub>GS</sub> to safe level, but this would result in increased IQ current.

To reduce the MOSFET conduction losses, lowest possible R<sub>DS(ON)</sub> is preferred, but selecting a MOSFET based on low R<sub>DS(ON)</sub> may not be beneficial always. Higher R<sub>DS(ON)</sub> will provide increased voltage information to LM74810-Q1's reverse comparator at a lower reverse current. Reverse current detection is better with increased R<sub>DS(ON)</sub>. Choosing a MOSFET with < 50-mV forward voltage drop at maximum current is a good starting point.

For active rectification of AC super imposed ripple on the battery supply voltage, gate-source charge Q<sub>GS</sub> of Q1 must be selected to meet the required AC ripple frequency. Maximum gate-source charge  $Q_{GS}$  (at 4.5-V  $V_{GS}$ ) for active rectification every cycle is

$$Q_{GS\_MAX} = \frac{2.5mA}{F_{AC\_RIPPLE}}$$

(6)

where 2.5 mA is minimum charge pump current at 7-V V<sub>DGATE</sub> - V<sub>A</sub>, F<sub>AC\_RIPPLE</sub> is frequency of the AC ripple superimposed on the battery and Q<sub>GS MAX</sub> is the Q<sub>GS</sub> value specified in manufacturer datasheet at 6-V V<sub>GS</sub>. For active rectification at  $F_{AC\_RIPPLE} = 30 \text{ KHz}$ ,  $Q_{GS\_MAX} = 83 \text{ nC}$ . Further for active rectification at  $F_{AC\_RIPPLE} = 200 \text{ me}$ KHz,  $Q_{GS MAX} = 12.5 nC$ .

Based on the design requirements, BUK9J0R9-40H MOSFET is selected and its ratings are:

- 40-V V<sub>DS(MAX)</sub> and 16-V V<sub>GS(MAX)</sub>

- $R_{DS(ON)}$  0.97-m  $\Omega$  typical at 4.5-V  $V_{GS}$  and 0.82 m  $\Omega$  rated at 10-V  $V_{GS}$

- MOSFET Q<sub>GS MAX</sub> 30.2 nC

Thermal resistance of the MOSFET should be considered against the expected maximum power dissipation in the MOSFET to ensure that the junction temperature (T<sub>.I</sub>) is well controlled.

#### 9.2.8 MOSFET Selection: Hot-Swap MOSFET Q2

The V<sub>DS</sub> rating of the MOSFET Q2 should be sufficient to handle the maximum system voltage along with the input transient voltage. For this 12-V design, transient over voltage events are during suppressed load dump 35 V 400 ms and ISO 7637-2 pulse 2 A 50 V for 50 µs. Further, ISO 7637-2 Pulse 3B is a very fast repetitive pulse of 100 V 100 ns that is usually absorbed by the input and output ceramic capacitors and the maximum voltage on the 12-V battery can be limited to < 40 V the minimum recommended input capacitance of 0.1 μF. The 50-V SO 7637-2 Pulse 2 A can also be absorbed by input and output capacitors and its amplitude could be reduced to

Copyright © 2021 Texas Instruments Incorporated

40-V peak by placing sufficient amount of capacitance at input and output. For this 12-V design, a 40-V  $V_{DS}$  rated MOSFET is selected.

The VGS rating of the MOSFET Q2 should be higher than that maximum HGATE-OUT voltage 15 V.

Inrush current through the MOSFET during input hot-plug into the 12-V battery is determined by output capacitance. External capacitor on HGATE,  $C_{DVDT}$  is used to limit the inrush current during input hot-plug or startup. The value of inrush current determined by 2 need to be selected to ensure that the MOSFET Q2 is operating well within its safe operating area (SOA). Considering  $C_{OUT}$  = 470  $\mu$ F and inrush current of 2.5 A, the calculated value of  $C_{DVDT}$  is 9.96 nF. Closest standard value of 10.0 nF is chosen for this design.

Duration of inrush current is calculated by

$$dT_{INRUSH} = \frac{12}{I_{INRUSH}} x C_{OUT} \tag{7}$$

Calculated inrush current duration is 2.36 ms with 2.5-A inrush current.

MOSFET BUK9J0R9-40H having 40-V  $V_{DS}$  and 16 V  $V_{GS}$  rating is selected for Q2. Power dissipation during inrush is well within the MOSFET's safe operating area (SOA).

#### 9.2.9 TVS selection

For 40-V rated MOSFET, two bi-directional 600-W SMBJ TVS, SMBJ33A and SMBJ16A are recommended for input transient clamping and protection. For detailed explanation on TVS selection for 12-V battery systems, refer to TVS Selection for 12-V Battery Systems and refer to TVS Selection for 24-V Battery Systems for 24-V battery systems.

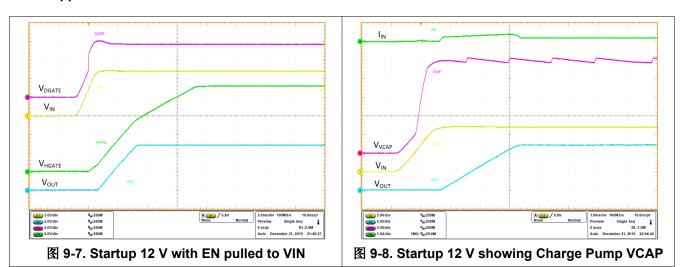

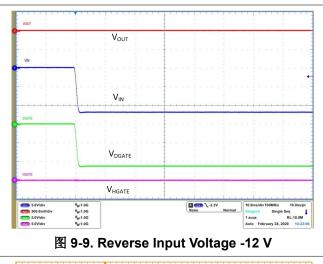

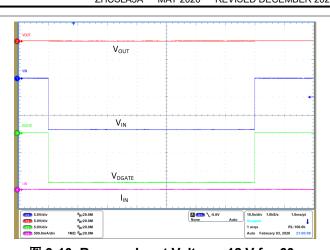

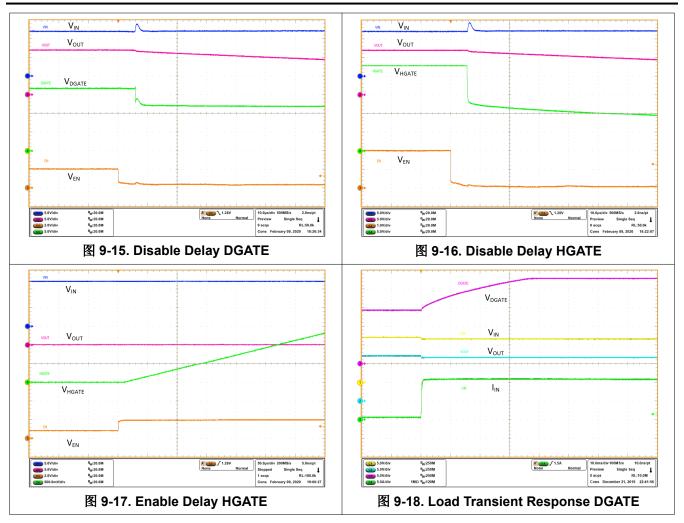

#### 9.2.10 Application Curves

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

$V_{\text{IN}}$

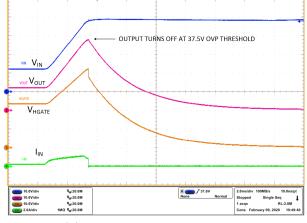

图 9-11. Over Voltage Cut-off

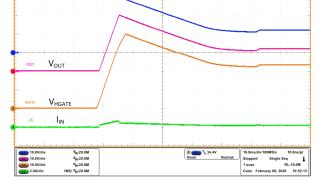

图 9-12. Over Voltage Recovery

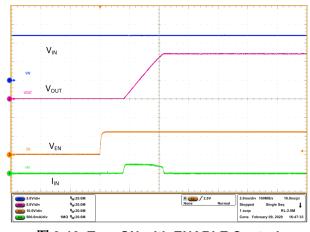

图 9-13. Turn ON with ENABLE Control

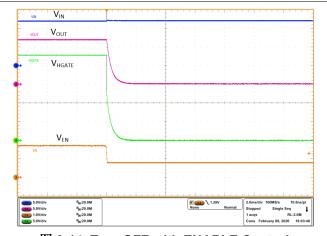

图 9-14. Turn OFF with ENABLE Control

### 9.3 Do's and Don'ts

Leave exposed pad (RTN) of the IC floating. Do not connect it to the GND plane. Connecting RTN to GND disables the Reverse Polarity protection feature.

# 10 Power Supply Recommendations

#### **10.1 Transient Protection**

When the external MOSFETs turn OFF during the conditions such as over voltage cut-off, reverse current blocking, EN/UVLO causing an interruption of the current flow, the input line inductance generates a positive voltage spike on the input and output inductance generates a negative voltage spike on the output. The peak amplitude of voltage spikes (transients) depends on the value of inductance in series to the input or output of the device. These transients can exceed the *Absolute Maximum Ratings* of the device if steps are not taken to address the issue.

Typical methods for addressing transients include:

- · Minimizing lead length and inductance into and out of the device

- Using large PCB GND plane

- · Use of a Schottky diode across the output and GND to absorb negative spikes

- A low value ceramic capacitor ( $C_{(IN)}$  to approximately 0.1  $\mu$  F) to absorb the energy and dampen the transients.

The approximate value of input capacitance can be estimated with 方程式 8.

$$V_{\text{spike(Absolute)}} = V_{\text{(IN)}} + I_{\text{(Load)}} \times \sqrt{\frac{L_{\text{(IN)}}}{C_{\text{(IN)}}}}$$

(8)

where

- V<sub>(IN)</sub> is the nominal supply voltage

- I<sub>(LOAD)</sub> is the load current

- L<sub>(IN)</sub> equals the effective inductance seen looking into the source

- C<sub>(IN)</sub> is the capacitance present at the input

Some applications may require additional Transient Voltage Suppressor (TVS) to prevent transients from exceeding the *Absolute Maximum Ratings* of the device. These transients can occur during EMC testing such as automotive ISO7637 pulses.

The circuit implementation with optional protection components (a ceramic capacitor, TVS and schottky diode) is shown in

■ 10-1

<sup>\*</sup> Optional components needed for suppression of transients

图 10-1. Circuit Implementation with Optional Protection Components for LM74810-Q1

### 10.2 TVS Selection for 12-V Battery Systems

In selecting the TVS, important specifications are breakdown voltage and clamping voltage. The breakdown voltage of the TVS+ should be higher than 24-V jump start voltage and 35-V suppressed load dump voltage and less than the maximum ratings of LM74810-Q1 (65 V). The breakdown voltage of TVS- should be beyond than maximum reverse battery voltage - 16 V, so that the TVS- is not damaged due to long time exposure to reverse connected battery.

Clamping voltage is the voltage the TVS diode clamps in high current pulse situations and this voltage is much higher than the breakdown voltage. In the case of an ISO 7637-2 pulse 1, the input voltage goes up to - 150 V with a generator impedance of 10  $\Omega$ . This translates to 15 A flowing through the TVS - and the voltage across the TVS would be close to its clamping voltage.

The next criterion is that the absolute maximum rating of cathode to anode voltage of the LM74810-Q1 (85 V) and the maximum V<sub>DS</sub> rating MOSFET are not exceeded. In the design example, 40-V rated MOSFET is chosen and maximum limit on the cathode to anode voltage is 40 V.

During ISO 7637-2 pulse 1, the anode of LM74810-Q1 is pulled down by the ISO pulse, clamped by TVS- and the MOSFET Q1 is turned off quickly to prevent reverse current from discharging the bulk output capacitors. When the MOSFET turns off, the cathode to anode voltage seen is equal to (TVS Clamping voltage + Output capacitor voltage). If the maximum voltage on output capacitor is 16 V (maximum battery voltage), then the clamping voltage of the TVS- should not exceed, (40 V - 16) V = -24 V.

On the positive side, the SMBJ33A TVS diode can be used for 12-V battery protection application. The breakdown voltage of 36.7 V meets the jump start, load dump requirements on the positive side. On the negative side, TVS has to withstand 16-V reverse battery connection and clamping voltage has to be - (40 V - 16 V) = -24 V. SMBJ16A can be used.

However if 60-V rated MOSFET is selected, a single bi-directional TVS SMBJ33CA is recommended. SMBJ series of TVS' are rated up to 600-W peak pulse power levels and are sufficient for ISO 7637-2 pulses.

#### 10.3 TVS Selection for 24-V Battery Systems

For 24-V battery protection application, the TVS and MOSFET Q1 and Q2 needs to be changed to suit 24-V battery requirements.

The breakdown voltage of the TVS+ should be higher than 48-V jump start voltage, less than the absolute maximum ratings of anode and enable pin of LM74810-Q1 (70 V) and should withstand 65-V suppressed load dump. The breakdown voltage of TVS- should be lower than maximum reverse battery voltage - 32 V, so that the TVS- is not damaged due to long time exposure to reverse connected battery.

During ISO 7637-2 pulse 1, the input voltage goes up to - 600 V with a generator impedance of 50 Ω. This translates to 12-A flowing through the TVS-. The clamping voltage of the TVS- cannot be same as that of 12-V battery protection circuit because during the ISO 7637-2 pulse, the Anode to Cathode voltage seen is equal to (-TVS Clamping voltage + Output capacitor voltage). For 24-V battery application, the maximum battery voltage is 32 V, then the clamping voltage of the TVS- should not exceed, 85 V - 32 V = 53 V.

Single bi-directional TVS cannot be used for 24-V battery protection because breakdown voltage for TVS+ ≥ 65V, maximum clamping voltage is ≤ 53 V and the clamping voltage cannot be less than the breakdown voltage. Two un-directional TVS connected back-back needs to be used at the input. For positive side TVS+, SMBJ58A with the breakdown voltage of 64.4 V (minimum), 67.8 (typical) is recommended. For the negative side TVS-, SMBJ28A with breakdown voltage close to 32 V (to withstand maximum reverse battery voltage - 32 V) and maximum clamping voltage of 42.1 V is recommended.

For 24-V battery protection, a 75-V rated MOSFET is recommended to be used along with SMBJ28A and SMBJ58A connected back-back at the input.

Product Folder Links: 1 M7481-Q1

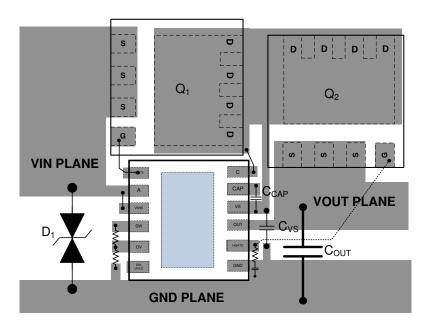

### 11 Layout

# 11.1 Layout Guidelines

- For the ideal diode stage, connect A, DGATE and C pins of LM74810-Q1 close to the MOSFET's SOURCE, GATE and DRAIN pins.

- For the load disconnect stage, connect HGATE and OUT pins of LM74810-Q1 close to the MOSFET's GATE and SOURCE pins.

- The high current path of for this solution is through the MOSFET, therefore it is important to use thick and short traces for source and drain of the MOSFET to minimize resistive losses.

- The DGATE pin of the LM74810-Q1 must be connected to the MOSFET GATE with short trace.

- Place transient suppression components close to LM74810-Q1.

- Place the decopuling capacitor, C<sub>VS</sub> close to VS pin and chip GND.

- The charge pump capacitor across CAP and VS pins must be kept away from the MOSFET to lower the thermal effects on the capacitance value.

- Obtaining acceptable performance with alternate layout schemes is possible, however the layout shown in the *Layout Example* is intended as a guideline and to produce good results.

# 11.2 Layout Example

图 11-1. PCB Layout Example

# 12 Device and Documentation Support

# 12.1 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

# 12.2 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 12.3 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

所有商标均为其各自所有者的财产。

#### 12.4 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 12.5 Glossary

**TI Glossary**

This glossary lists and explains terms, acronyms, and definitions.

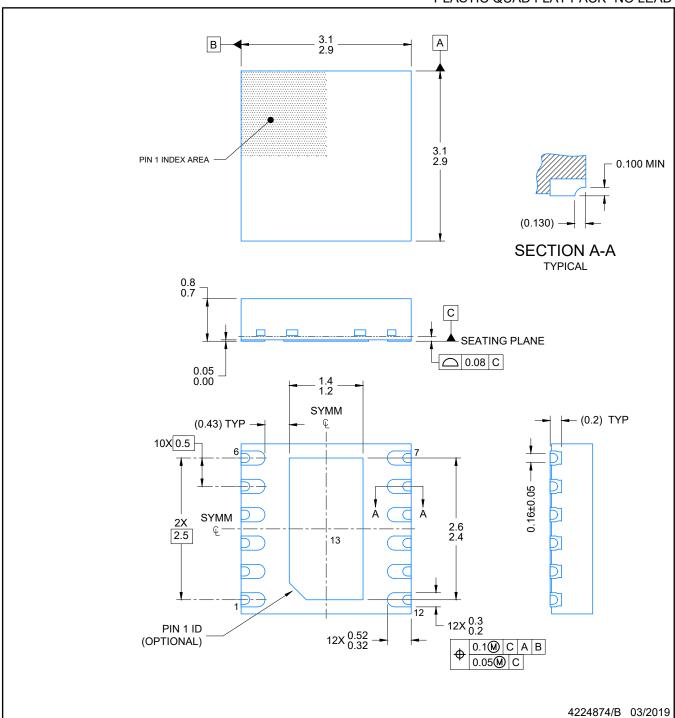

# 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Product Folder Links: / M7481-Q1

# 重要声明和免责声明

TI 提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将独自承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保或其他要求。这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款 () 或 TI.com.cn 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020,德州仪器 (TI) 公司

# PACKAGE OPTION ADDENDUM

25-Jan-2021

#### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

| LM74810QDRRRQ1   | ACTIVE     | WSON         | DRR                | 12   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | L74810               | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4223490/A

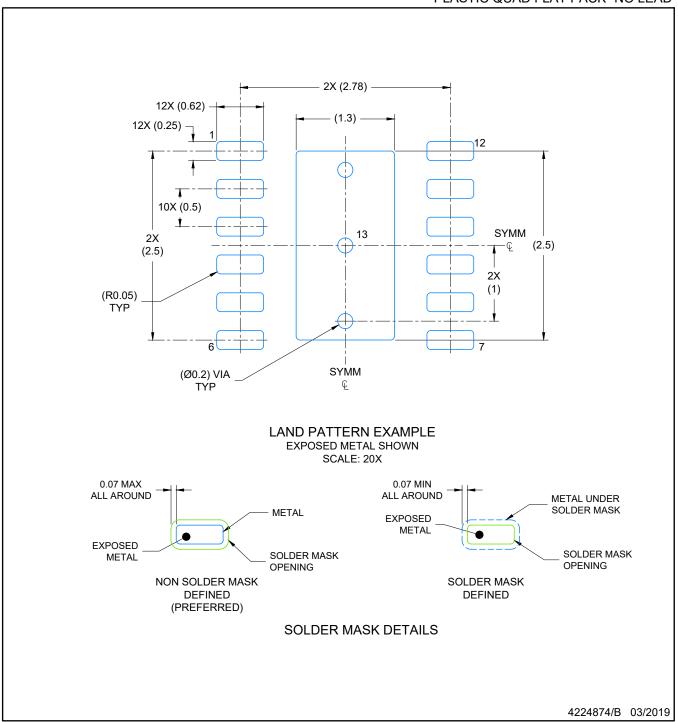

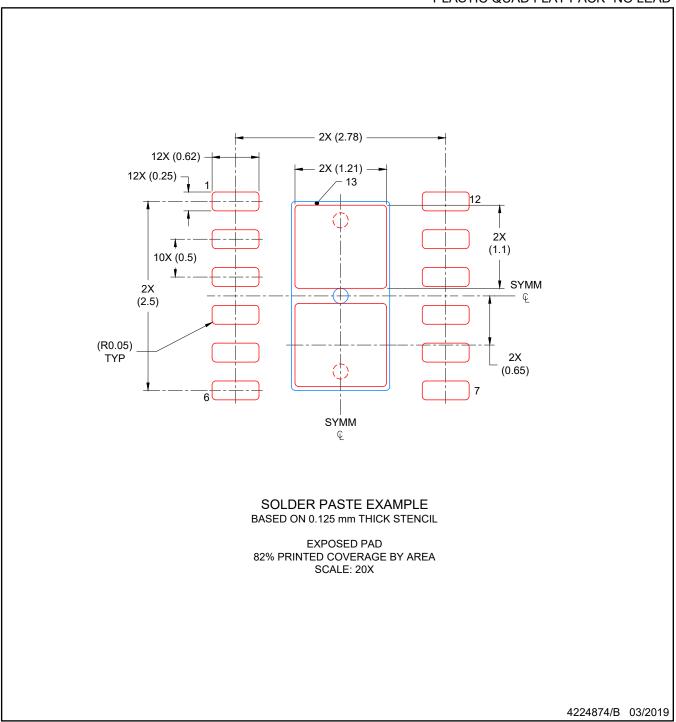

PLASTIC QUAD FLAT PACK- NO LEAD

#### NOTES: