# TPS51275, TPS51275B, TPS51275C

#### www.ti.com.cn

#### ZHCS982B - JUNE 2012 - REVISED MARCH 2013

# 具有 5V 和 3.3V 低压降稳压器 (LDO) 双路同步,降压控制器

# 特性

- 输入电压范围: 5V 至 24V

- 输出电压: 5V 和 3.3V (可调范围 ±10%)

- 内置,100mA,5V和3.3V LDO

- 用于电荷泵的时钟输出 •

- **±1%** 基准精度

- 自适应接通时间 D-CAP™ 模式控制架构,此架构 • 支持 300kHz 和 355kHz 频率设置

- 自动跳跃轻负载运行 (**TPS51275** 和 **TPS51275C**)

- OOA 轻负载运行 (TPS51275B)

- 内部 0.8ms 电压伺服器软启动 •

- 低侧 R<sub>DS(on)</sub>电流感测机制

- 内置输出放电功能 .

- 用于开关的独立使能输入 •

- 专用 OC 设置端子

- 电源正常指示器 •

- 过压 (OVP), 欠压 (UVP) 和过流 (OCP) 保护

- 非锁存欠压闭锁 (UVLO) 和过热 (OTP) 保护 •

- 20 引脚, 3mm x 3mm, 四方扁平无引线 • (QFN)(RUK) 封装

# 应用范围

- 笔记本电脑

- 平板电脑 •

# 说明

TPS51275, TPS51275B 和 TPS51275C 是针对笔记 本系统电源解决方案的经济型,双路同步降压控制器。 它提供 5V 和 3.3V LDO 并且只需要使用极少的外部组 件。 260kHz VCLK 输出可被用于驱动一个外部电荷 泵,为负载开关生成栅极驱动电压而不会降低主转换器 的效率。TPS51275, TPS51275B 和 TPS51275C 支 持高效,快速瞬态响应并提供一个组合电源正常信号。 自适应接通时间, D-CAP™ 控制提供便捷且有效的运 行。此器件运行电源输入电压范围介于 5V 至 24V 之 间并且支持 5.0V 和 3.3V 的输出电压。 TPS51275, TPS51275B 和 TPS51275C 采用 20 引 脚, 3mm x 3mm, QFN 封装, 额定运行温度 -40℃

至 85°C。

## 订购信息(1)

| 可订购的<br>器件号   | 使能<br>功能  | 跳跃模式    | 常开模式 - LDO    | 封装       | 输出电源 | 数量   |

|---------------|-----------|---------|---------------|----------|------|------|

| TPS51275RUKR  | EN1 和 EN2 | 스카메띠    | VREG3         |          | 卷带封装 | 3000 |

| TPS51275RUKT  |           | 自动跳跃    | VREGS         | 塑料四方扁平封装 | 小型卷带 | 250  |

| TPS51275BRUKR |           | OOA     | VREG3 和 VREG5 |          | 卷带封装 | 3000 |

| TPS51275BRUKT |           |         |               |          | 小型卷带 | 250  |

| TPS51275CRUKR |           | 古二ム国地口で |               |          | 卷带封装 | 3000 |

| TPS51275CRUKT |           | 自动跳跃    |               |          | 小型卷带 | 250  |

(1) 要获得最新的封装和订购信息,请见本文档末尾的封装选项附录,或者访问 TI 网站 www.ti.com。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. D-CAP is a trademark of Texas Instruments.

ZHCS982B-JUNE 2012-REVISED MARCH 2013

www.ti.com.cn

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

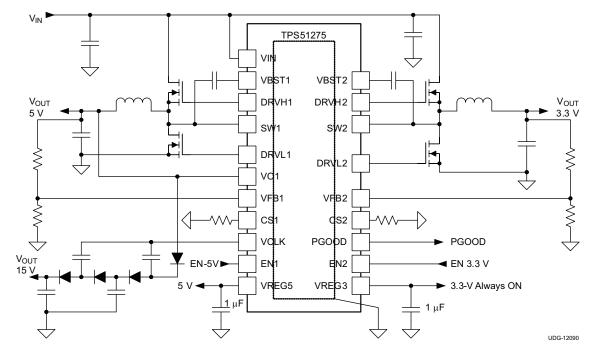

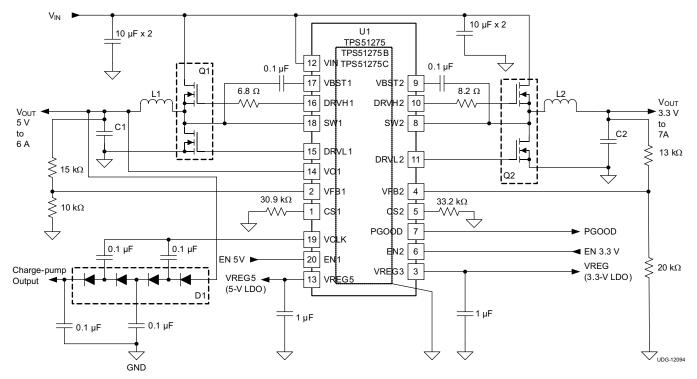

# **TYPICAL APPLICATION DIAGRAM (TPS51275)**

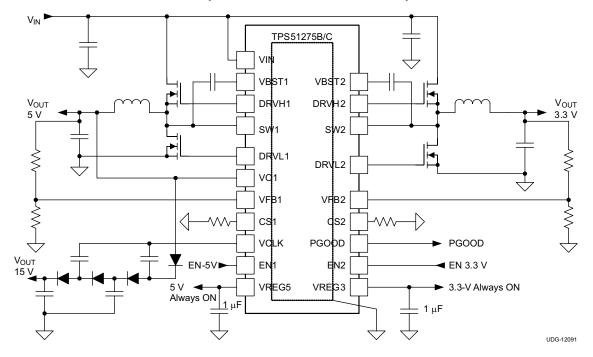

# **TYPICAL APPLICATION DIAGRAM (TPS51275B and TPS51275C)**

ZHCS982B - JUNE 2012 - REVISED MARCH 2013

#### www.ti.com.cn

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                      |                                                                     | VAL  | VALUE |      |

|--------------------------------------|---------------------------------------------------------------------|------|-------|------|

|                                      |                                                                     | MIN  | MAX   | UNIT |

|                                      | VBST1, VBST2                                                        | -0.3 | 32    |      |

|                                      | VBST1, VBST2 <sup>(3)</sup>                                         | -0.3 | 6     |      |

|                                      | SW1, SW2                                                            | -6.0 | 26    |      |

| Input voltage <sup>(2)</sup>         | VIN                                                                 | -0.3 | 26    | V    |

|                                      | EN1, EN2                                                            | -0.3 | 6     |      |

|                                      | VFB1, VFB2                                                          | -0.3 | 3.6   |      |

|                                      | VO1                                                                 | -0.3 | 6     |      |

|                                      | DRVH1, DRVH2                                                        | -6.0 | 32    |      |

|                                      | DRVH1, DRVH2 <sup>(3)</sup>                                         | -0.3 | 6     |      |

|                                      | DRVH1, DRVH2 <sup>(3)</sup> (pulse width < 20 ns)                   |      | 6     | l    |

| Output voltage <sup>(2)</sup>        | DRVL1, DRVL2                                                        | -0.3 | 6     | V    |

|                                      | DRVL1, DRVL2 (pulse width < 20 ns)                                  | -2.5 | 6     |      |

|                                      | PGOOD, VCLK, VREG5                                                  |      | 6     |      |

|                                      | VREG3, CS1, CS2                                                     | -0.3 | 3.6   |      |

| Electrostatio discharge              | HBM QSS 009-105 (JESD22-A114A)<br>CDM QSS 009-147 (JESD22-C101B.01) |      | 2     | kV   |

| Electrostatic discharge              |                                                                     |      | 1     | ĸν   |

| Junction temperature, T <sub>J</sub> |                                                                     | 150  |       | °C   |

| Storage temperature, T <sub>ST</sub> |                                                                     | -55  | 150   | °C   |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to the network ground terminal unless otherwise noted

(3) Voltage values are with respect to SW terminals.

#### THERMAL INFORMATION

|                         | THERMAL METRIC <sup>(1)</sup>                | TPS51275<br>TPS51275B<br>TPS51275C | UNITS |

|-------------------------|----------------------------------------------|------------------------------------|-------|

|                         |                                              | 20-PIN RUK                         | -     |

| θ <sub>JA</sub>         | Junction-to-ambient thermal resistance       | 94.1                               |       |

| θ <sub>JCtop</sub>      | Junction-to-case (top) thermal resistance    | 58.1                               |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 64.3                               | °C/W  |

| ΨJT                     | Junction-to-top characterization parameter   | 31.8                               | C/VV  |

| $\Psi_{JB}$             | Junction-to-board characterization parameter | 58.0                               |       |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | 5.9                                |       |

(1) 有关传统和新的热度量的更多信息,请参阅IC 封装热度量应用报告, SPRA953。

ZHCS982B-JUNE 2012-REVISED MARCH 2013

www.ti.com.cn

# **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                                                               |                                                | MIN  | TYP MAX | UNIT |

|---------------------------------------------------------------|------------------------------------------------|------|---------|------|

| Supply voltage                                                | VIN                                            | 5    | 24      |      |

|                                                               | VBST1, VBST2                                   | -0.1 | 30      |      |

|                                                               | VBST1, VBST2 <sup>(2)</sup>                    | -0.1 | 5.5     |      |

| Input voltogo (1)                                             | SW1, SW2                                       | -5.5 | 24      | V    |

| Input voltage <sup>(1)</sup><br>Output voltage <sup>(1)</sup> | EN1, EN2                                       | -0.1 | 5.5     |      |

|                                                               | VFB1, VFB2                                     | -0.1 | 3.5     |      |

|                                                               | VO1                                            | -0.1 | 5.5     |      |

|                                                               | DRVH1, DRVH2                                   | -5.5 | 30      |      |

|                                                               | DRVH1, DRVH2 <sup>(2)</sup>                    | -0.1 | 5.5     |      |

|                                                               | DRVL1, DRVL2<br>PGOOD, VCLK, VREG5             |      | 5.5     | V    |

|                                                               |                                                |      | 5.5     |      |

|                                                               | VREG3, CS1, CS2                                | -0.1 | 3.5     |      |

| Operating free-air                                            | Operating free-air temperature, T <sub>A</sub> |      | 85      | °C   |

All voltage values are with respect to the network ground terminal unless otherwise noted.

Voltage values are with respect to the SW terminal.

ZHCS982B - JUNE 2012 - REVISED MARCH 2013

www.ti.com.cn

# **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range,  $V_{VIN}$ = 12 V,  $V_{VO1}$ = 5 V,  $V_{VFB1}$ =  $V_{VFB2}$ = 2 V,  $V_{EN1}$ =  $V_{EN2}$ = 3.3 V (unless otherwise noted)

|                                   | PARAMETER                      | TEST CONDITION                                                                                                      | MIN   | TYP   | MAX   | UNIT |  |

|-----------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|--|

| SUPPLY C                          | URRENT                         | ·                                                                                                                   |       |       |       |      |  |

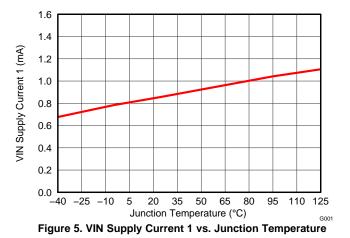

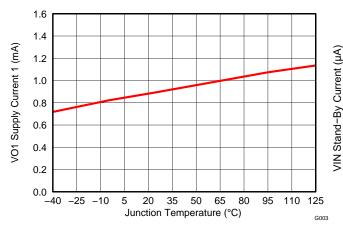

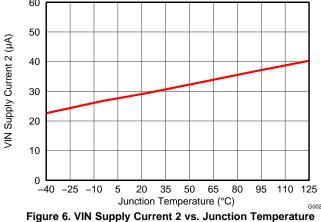

| I <sub>VIN1</sub>                 | VIN supply current-1           | $T_A = 25^{\circ}C$ , No load, $V_{VO1}=0$ V                                                                        |       | 860   |       | μA   |  |

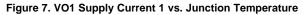

| I <sub>VIN2</sub>                 | VIN supply current-2           | $T_A = 25^{\circ}C$ , No load                                                                                       |       | 30    |       | μA   |  |

| I <sub>VO1</sub>                  | VO1 supply current             | $T_A = 25^{\circ}C$ , No load, $V_{VFB1} = V_{VFB2} = 2.05 V$                                                       |       | 900   |       | μA   |  |

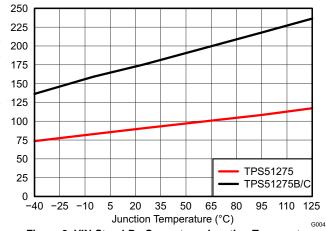

| IVIN(STBY)                        | VIN stand-by current TPS51275  | $T_A = 25^{\circ}C$ , No load, $V_{VO1} = 0$ V, $V_{EN1} = V_{EN2} = 0$ V                                           |       | 95    |       | μA   |  |

| I <sub>VIN(STBY)</sub>            | VIN stand-by current           | $T_A = 25^{\circ}$ C, No load, V <sub>VO1</sub> =0 V, V <sub>EN1</sub> =V <sub>EN2</sub> =0V (<br>TPS51275B/C)      |       | 180   |       | μΑ   |  |

| INTERNAL                          | REFERENCE                      |                                                                                                                     |       |       |       |      |  |

|                                   |                                | $T_A = 25^{\circ}C$                                                                                                 | 1.99  | 2.00  | 2.01  | V    |  |

| V <sub>FBx</sub>                  | VFB regulation voltage         |                                                                                                                     | 1.98  | 2.00  | 2.02  | V    |  |

| VREG5 OU                          | ITPUT                          |                                                                                                                     |       |       |       |      |  |

|                                   |                                | $T_A = 25^{\circ}C$ , No load, $V_{VO1} = 0 V$                                                                      | 4.9   | 5.0   | 5.1   |      |  |

|                                   |                                | V <sub>VIN</sub> > 7 V , V <sub>VO1</sub> = 0 V, I <sub>VREG5</sub> < 100 mA                                        | 4.85  | 5.00  | 5.10  | Ň    |  |

| V <sub>VREG5</sub> \              | VREG5 output voltage           | $V_{VIN} > 5.5 \text{ V}$ , $V_{VO1}$ = 0 V, $I_{VREG5}$ < 35 mA                                                    | 4.85  | 5.00  | 5.10  | V    |  |

|                                   |                                | $V_{VIN} > 5 \text{ V}, V_{VO1} = 0 \text{ V}, I_{VREG5} < 20 \text{ mA}$                                           | 4.50  | 4.75  | 5.10  |      |  |

| I <sub>VREG5</sub>                | VREG5 current limit            | V <sub>VO1</sub> = 0 V, V <sub>VREG5</sub> = 4.5 V, V <sub>VIN</sub> = 7 V                                          | 100   | 150   |       | mA   |  |

| R <sub>V5SW</sub>                 | 5-V switch resistance          | $T_A = 25^{\circ}C, V_{VO1} = 5 V, I_{VREG5} = 50 mA$                                                               |       | 1.8   |       | Ω    |  |

| VREG3 OU                          | ITPUT                          |                                                                                                                     |       |       |       |      |  |

|                                   |                                | No load, $V_{VO1}$ = 0 V, $T_A$ = 25°C                                                                              | 3.267 | 3.300 | 3.333 |      |  |

|                                   |                                | $V_{VIN} > 7 V$ , $V_{VO1}$ = 0 V, $I_{VREG3}$ < 100 mA                                                             | 3.217 | 3.300 | 3.383 |      |  |

|                                   |                                | 5.5 V < V <sub>VIN</sub> , V <sub>VO1</sub> = 0 V, I <sub>VREG3</sub> < 35 mA                                       | 3.234 | 3.300 | 3.366 |      |  |

| V <sub>VREG3</sub>                | VREG3 output voltage           | 0°C $\leq$ T_A $\leq$ 85°C, V_{VIN} $>$ 5.5 V, V_{VO1} = 0 V, I_{VREG3} < 35 mA                                     | 3.267 | 3.300 | 3.333 | V    |  |

|                                   |                                | 0°C $\leq$ T <sub>A</sub> $\leq$ 85°C, V <sub>VIN</sub> > 5.5 V, V <sub>VO1</sub> = 5 V, I <sub>VREG3</sub> < 35 mA | 3.267 | 3.300 | 3.333 |      |  |

|                                   |                                | $V_{VIN} > 5 \text{ V}, V_{VO1} = 0 \text{ V}, I_{VREG3} < 35 \text{ mA}$                                           | 3.217 | 3.300 | 3.366 |      |  |

| I <sub>VREG3</sub>                | VREG3 current limit            | V <sub>VO1</sub> = 0 V, V <sub>VREG3</sub> = 3.0 V, V <sub>VIN</sub> = 7 V                                          | 100   | 150   |       | mA   |  |

| DUTY CYC                          | LE and FREQUENCY CONTROL       |                                                                                                                     |       |       | ·     |      |  |

| f <sub>sw1</sub>                  | CH1 frequency <sup>(1)</sup>   | T <sub>A</sub> = 25°C, V <sub>VIN</sub> = 20 V                                                                      | 240   | 300   | 360   | kHz  |  |

| f <sub>SW2</sub>                  | CH2 frequency <sup>(1)</sup>   | T <sub>A</sub> = 25°C, V <sub>VIN</sub> = 20 V                                                                      | 280   | 355   | 430   | kHz  |  |

| t <sub>OFF(MIN)</sub>             | Minimum off-time               | $T_A = 25^{\circ}C$                                                                                                 | 200   | 300   | 500   | ns   |  |

| MOSFET D                          | PRIVERS                        |                                                                                                                     |       |       | ·     |      |  |

| Р                                 |                                | Source, $(V_{VBST} - V_{DRVH}) = 0.25 \text{ V}, (V_{VBST} - V_{SW}) = 5 \text{ V}$                                 |       | 3.0   |       | 0    |  |

| R <sub>DRVH</sub>                 | DRVH resistance                | Sink, $(V_{DRVH} - V_{SW}) = 0.25 \text{ V}, (V_{VBST} - V_{SW}) = 5 \text{ V}$                                     | 1.9   |       |       | Ω    |  |

| Р                                 |                                | Source, $(V_{VREG5} - V_{DRVL}) = 0.25 \text{ V}, V_{VREG5} = 5 \text{ V}$                                          |       | 3.0   |       | -    |  |

| R <sub>DRVL</sub> DRVL resistance |                                | Sink, V <sub>DRVL</sub> = 0.25 V, V <sub>VREG5</sub> = 5 V                                                          | 0.9   |       |       | Ω    |  |

|                                   | Dood time                      | DRVH-off to DRVL-on                                                                                                 |       | 12    |       |      |  |

| t <sub>D</sub>                    | Dead time                      | DRVL-off to DRVH-on 20                                                                                              |       |       |       | ns   |  |

| INTERNAL                          | BOOT STRAP SWITCH              |                                                                                                                     |       |       |       |      |  |

| R <sub>VBST (ON)</sub>            | Boost switch on-resistance     | $T_A = 25^{\circ}C$ , $I_{VBST} = 10 \text{ mA}$                                                                    |       | 13    |       | Ω    |  |

| IVBSTLK                           | VBST leakage current           | $T_A = 25^{\circ}C$                                                                                                 |       |       | 1     | μA   |  |

| CLOCK OL                          | JTPUT                          |                                                                                                                     |       |       |       |      |  |

| R <sub>VCLK (PU)</sub>            | VCLK on-resistance (pull-up)   | $T_A = 25^{\circ}C$                                                                                                 |       | 10    |       | ~    |  |

| R <sub>VCLK (PD)</sub>            | VCLK on-resistance (pull-down) | T <sub>A</sub> = 25°C                                                                                               |       | 10    |       | Ω    |  |

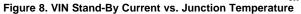

| f <sub>CLK</sub>                  | Clock frequency                | $T_A = 25^{\circ}C$                                                                                                 |       | 260   |       | kHz  |  |

(1) Ensured by design. Not production tested.

ZHCS982B-JUNE 2012-REVISED MARCH 2013

# **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range,  $V_{VIN}$ = 12 V,  $V_{VO1}$ = 5 V,  $V_{VFB1}$ =  $V_{VFB2}$ = 2 V,  $V_{EN1}$ =  $V_{EN2}$ = 3.3 V (unless otherwise noted)

|                       | PARAMETER                                         |      | TEST CONDITION                                                                 | MIN    | ТҮР    | MAX    | UNIT   |

|-----------------------|---------------------------------------------------|------|--------------------------------------------------------------------------------|--------|--------|--------|--------|

| OUTPUT D              | ISCHARGE                                          |      |                                                                                | •      |        |        |        |

| R <sub>DIS1</sub>     | CH1 discharge resistance                          |      | T <sub>A</sub> = 25°C, V <sub>VO1</sub> = 0.5 V                                |        | 35     |        | Ω      |

| -                     |                                                   |      | $V_{\text{EN1}} = V_{\text{EN2}} = 0 \text{ V}$                                |        |        |        |        |

| R <sub>DIS2</sub>     | CH2 discharge resistance TPS5                     | 1275 |                                                                                |        | 75     |        | Ω      |

| R <sub>DIS2</sub>     | CH2 discharge resistance                          |      | $T_A = 25^{\circ}C, V_{SW2} = 0.5 V, V_{EN1} = V_{EN2} = 0 V$<br>(TPS51275B/C) |        | 70     |        | Ω      |

| SOFT STAR             | RT OPERATION                                      |      | 1                                                                              |        |        |        |        |

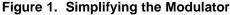

| t <sub>SS</sub>       | Soft-start time                                   |      | From ENx="Hi" and $V_{VREG5} > V_{UVLO5}$ to $V_{OUT} = 95\%$                  |        | 0.91   |        | ms     |

| t <sub>SSRAMP</sub>   | Soft-start time (ramp-up)                         |      | $V_{OUT}$ = 0% to $V_{OUT}$ = 95%, $V_{VREG5}$ = 5 V                           |        | 0.78   |        | ms     |

| POWER GO              | DOD                                               |      |                                                                                |        |        |        |        |

|                       |                                                   |      | Lower (rising edge of PG-in)                                                   | 92.5%  | 95.0%  | 97.5%  |        |

| V                     | PG threshold                                      |      | Hysteresis                                                                     |        | 5%     |        |        |

| V <sub>PGTH</sub>     | r G threshold                                     |      | Upper (rising edge of PG-out)                                                  | 107.5% | 110.0% | 112.5% | 1      |

|                       |                                                   |      | Hysteresis                                                                     |        | 5%     |        | 1      |

| I <sub>PGMAX</sub>    | PG sink current                                   |      | $V_{PGOOD} = 0.5 V$                                                            |        | 6.5    |        | mA     |

| I <sub>PGLK</sub>     | PG leak current                                   |      | V <sub>PGOOD</sub> = 5.5 V                                                     |        |        | 1      | μA     |

| t <sub>PGDEL</sub>    | PG delay                                          |      | From PG lower threshold (95%=typ) to PG flag high                              |        | 0.7    |        | ms     |

| CURRENT               | SENSING                                           |      |                                                                                |        |        |        |        |

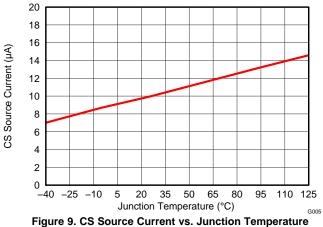

| I <sub>CS</sub>       | CS source current                                 |      | $T_A = 25^{\circ}C, V_{CS} = 0.4 V$                                            | 9      | 10     | 11     | μΑ     |

| TC <sub>CS</sub>      | CS current temperature coefficient <sup>(1)</sup> |      | On the basis of 25°C                                                           |        | 4500   |        | ppm/°C |

| V <sub>CS</sub>       | CS Current limit setting range                    |      |                                                                                | 0.2    |        | 2      | V      |

| V <sub>ZC</sub>       | Zero cross detection offset                       |      | T <sub>A</sub> = 25°C                                                          | -1     | 1      | 3      | mV     |

| LOGIC THE             | RESHOLD                                           |      |                                                                                | 1      |        |        |        |

| V <sub>ENX(ON)</sub>  | EN threshold high-level                           |      | SMPS on level                                                                  |        |        | 1.6    | V      |

| V <sub>ENX(OFF)</sub> | EN threshold low-level                            |      | SMPS off level                                                                 | 0.3    |        |        | V      |

| I <sub>EN</sub>       | EN input current                                  |      | V <sub>ENx</sub> = 3.3 V                                                       | -1     |        | 1      | μA     |

| OUTPUT O              | VERVOLTAGE PROTECTION                             |      | •                                                                              |        |        |        |        |

| V <sub>OVP</sub>      | OVP trip threshold                                |      |                                                                                | 112.5% | 115.0% | 117.5% |        |

| t <sub>OVPDLY</sub>   | OVP propagation delay                             |      | $T_A = 25^{\circ}C$                                                            |        | 0.5    |        | μs     |

| OUTPUT U              | NDERVOLTAGE PROTECTION                            |      |                                                                                | 1      |        |        |        |

| V <sub>UVP</sub>      | UVP trip Threshold                                |      |                                                                                | 55%    | 60%    | 65%    |        |

| t <sub>UVPDLY</sub>   | UVP prop delay                                    |      |                                                                                |        | 250    |        | μs     |

| t <sub>UVPENDLY</sub> | UVP enable delay                                  |      | From ENx ="Hi", V <sub>VREG5</sub> = 5 V                                       |        | 1.35   |        | ms     |

| UVLO                  |                                                   |      |                                                                                | 1      |        |        |        |

|                       |                                                   |      | Wake up                                                                        |        | 4.58   |        | V      |

| V <sub>UVLOVIN</sub>  | VIN UVLO Threshold                                |      | Hysteresis                                                                     |        | 0.5    |        | V      |

|                       |                                                   |      | Wake up                                                                        |        | 4.38   | 4.50   | V      |

| V <sub>UVLO5</sub>    | VREG5 UVLO Threshold                              |      | Hysteresis                                                                     |        | 0.4    |        | V      |

|                       |                                                   |      | Wake up                                                                        |        | 3.15   |        | V      |

| V <sub>UVLO3</sub>    | VREG3 UVLO Threshold                              |      | Hysteresis                                                                     |        | 0.15   |        | V      |

| OVER TEM              | IPERATURE PROTECTION                              |      | 1                                                                              |        |        |        |        |

|                       |                                                   |      | Shutdown temperature                                                           |        | 155    |        |        |

| T <sub>OTP</sub>      | OTP threshold <sup>(1)</sup>                      |      | Hysteresis                                                                     |        | 10     |        | °C     |

(1) Ensured by design. Not production tested.

#### ZHCS982B - JUNE 2012 - REVISED MARCH 2013

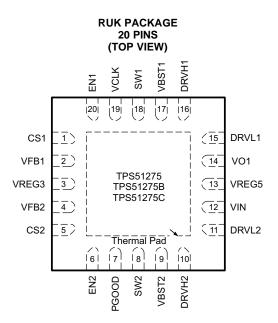

# **DEVICE INFORMATION**

#### **PIN FUNCTIONS**

| PIN NO.     |                                          |   |                                                                                                                          |  |  |  |  |  |

|-------------|------------------------------------------|---|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME        | E TPS51275 I/O<br>TPS51275B<br>TPS51275C |   | DESCRIPTION                                                                                                              |  |  |  |  |  |

| CS1         | 1                                        | 0 | Sets the channel 1 OCL trip level.                                                                                       |  |  |  |  |  |

| CS2         | 5                                        | 0 | Sets the channel 2OCL trip level.                                                                                        |  |  |  |  |  |

| DRVH1       | 16                                       | 0 | High-side driver output                                                                                                  |  |  |  |  |  |

| DRVH2       | 10                                       | 0 | High-side driver output                                                                                                  |  |  |  |  |  |

| DRVL1       | 15                                       | 0 | Low-side driver output                                                                                                   |  |  |  |  |  |

| DRVL2       | 11                                       | 0 | Low-side driver output                                                                                                   |  |  |  |  |  |

| EN1         | 20                                       | I | Channel 1 enable.                                                                                                        |  |  |  |  |  |

| EN2         | 6                                        | Ι | Channel 2 enable.                                                                                                        |  |  |  |  |  |

| PGOOD       | 7                                        | 0 | Power good output flag. Open drain output. Pull up to external rail via a resistor                                       |  |  |  |  |  |

| SW1         | 18                                       | 0 | Switch-node connection.                                                                                                  |  |  |  |  |  |

| SW2         | 8                                        | 0 | Switch-node connection.                                                                                                  |  |  |  |  |  |

| VBST1       | 17                                       | I | Supply input for high-side MOSFET (bootstrap terminal). Connect capacitor from this pin to SW                            |  |  |  |  |  |

| VBST2       | 9                                        | Ι | terminal.                                                                                                                |  |  |  |  |  |

| VCLK        | 19                                       | 0 | Clock output for charge pump.                                                                                            |  |  |  |  |  |

| VFB1        | 2                                        | I |                                                                                                                          |  |  |  |  |  |

| VFB2        | 4                                        | I | Voltage feedback Input                                                                                                   |  |  |  |  |  |

| VIN         | 12                                       | Т | Power conversion voltage input. Apply the same voltage as drain voltage of high-side MOSFETs of channel 1 and channel 2. |  |  |  |  |  |

| VO1         | 14                                       | Ι | Output voltage input, 5-V input for switch-over.                                                                         |  |  |  |  |  |

| VREG3       | 3                                        | 0 | 3.3-V LDO output.                                                                                                        |  |  |  |  |  |

| VREG5       | 13                                       | 0 | 5-V LDO output.                                                                                                          |  |  |  |  |  |

| Thermal pad |                                          |   | GND terminal, solder to the ground plane                                                                                 |  |  |  |  |  |

# ZHCS982B-JUNE 2012-REVISED MARCH 2013

ZHCS982B - JUNE 2012 - REVISED MARCH 2013

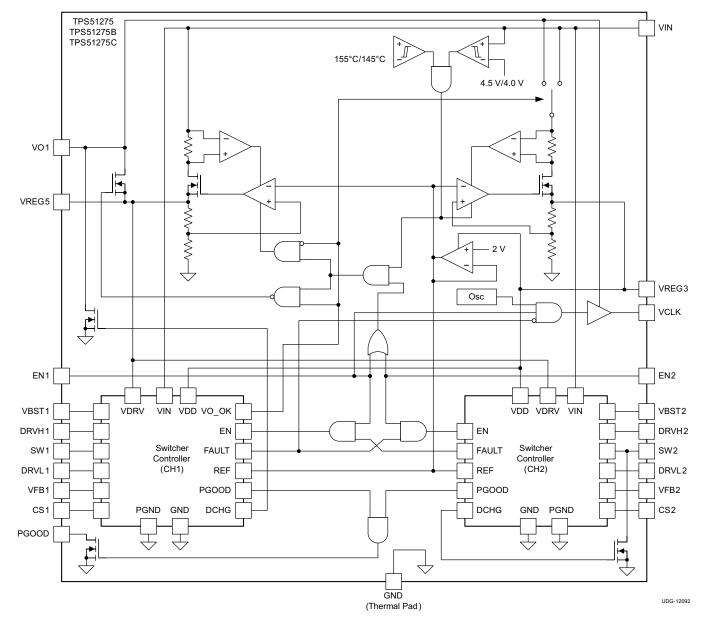

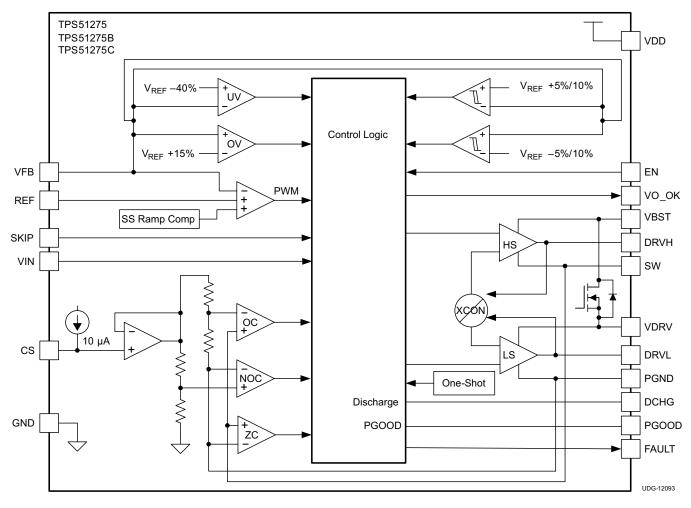

# SWITCHER CONTROLLER BLOCK DIAGRAM

ZHCS982B-JUNE 2012-REVISED MARCH 2013

www.ti.com.cn

# DETAILED DESCRIPTION

### **PWM Operations**

The main control loop of the switch mode power supply (SMPS) is designed as an adaptive on-time pulse width modulation (PWM) controller. It supports a proprietary D-CAP<sup>™</sup> mode. D-CAP<sup>™</sup> mode does not require external conpensation circuit and is suitable for low external component count configuration when used with appropriate amount of ESR at the output capacitor(s).

At the beginning of each cycle, the synchronous high-side MOSFET is turned on, or enters the ON state. This MOSFET is turned off, or enters the 'OFF state, after the internal, one-shot timer expires. The MOSFET is turned on again when the feedback point voltage, V<sub>VFB</sub>, decreased to match the internal 2-V reference. The inductor current information is also monitored and should be below the overcurrent threshold to initiate this new cycle. By repeating the operation in this manner, the controller regulates the output voltage. The synchronous low-side (rectifying) MOSFET is turned on at the beginning of each OFF state to maintain a minimum of conduction loss. The low-side MOSFET is turned off before the high-side MOSFET turns on at next switching cycle or when inductor current information detects zero level. This enables seamless transition to the reduced frequency operation during light-load conditions so that high efficiency is maintained over a broad range of load current.

## Adaptive On-Time/ PWM Frequency Control

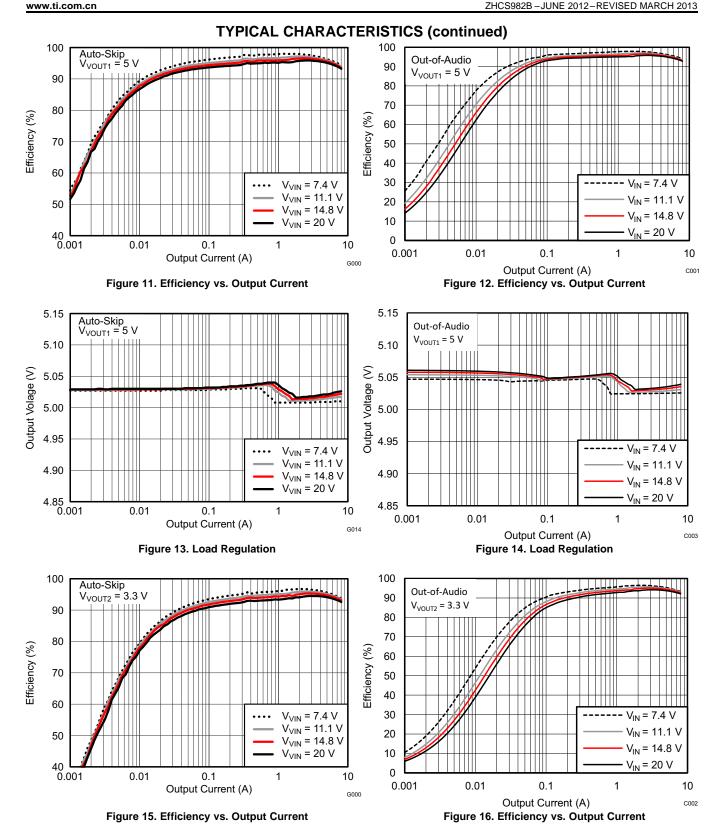

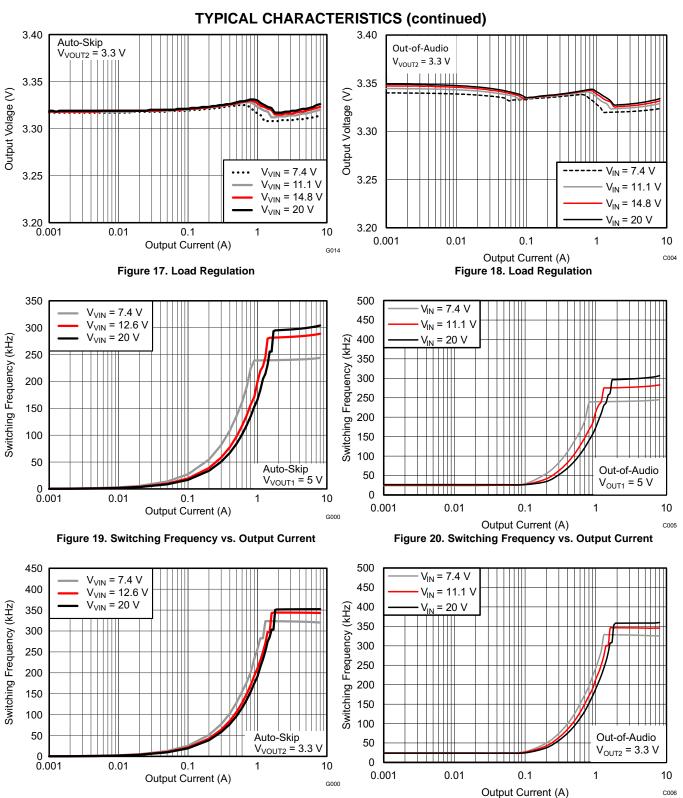

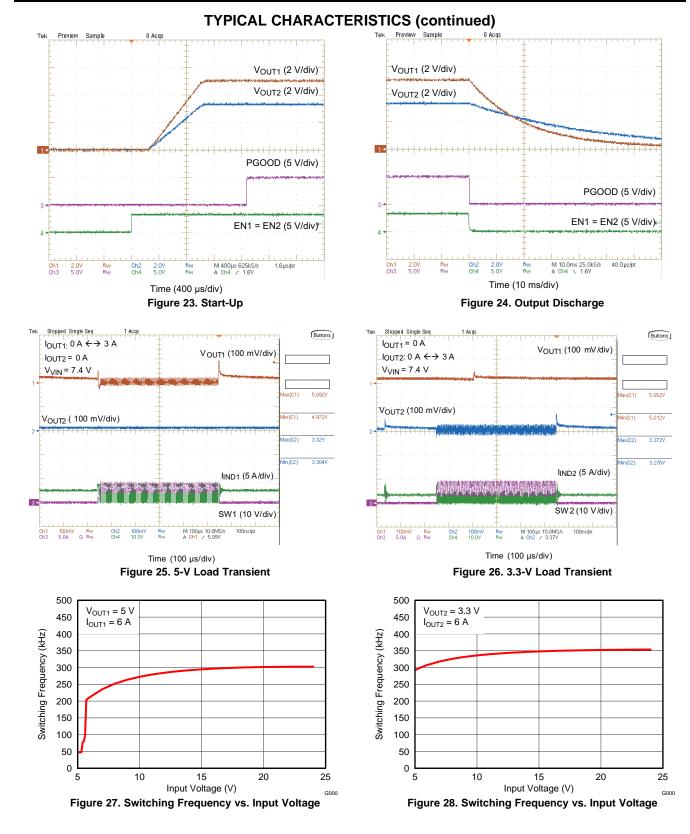

Because the TPS51275/B/C does not have a dedicated oscillator for control loop on board, switching cycle is controlled by the adaptive on-time circuit. The on-time is controlled to meet the target switching frequency by feed-forwarding the input and output voltage into the on-time one-shot timer. The target switching frequency is varied according to the input voltage to achieve higher duty operation for lower input voltage application. The switching frequency of CH1 (5-V output) is 300 kHz during continuous conduction mode (CCM) operation when  $V_{IN} = 20$  V. The CH2 (3.3-V output) is 355 kHz during CCM when  $V_{IN} = 20$  V. (See Figure 27 and Figure 28).

To improve load transient performance and load regulation in lower input voltage conditions, TPS51275/B/C can extend the on-time. The maximum on-time extension of CH1 is 4 times for CH2 is 3 times. To maintain a reasonable inductor ripple current during on-time extension, the inductor ripple current should be set to less than half of the OCL (valley) threshold. (See Step 2. Choose the Inductor). The on-time extension function provides high duty cycle operation and shows better DC (static) performance. AC performance is determined mostly by the output LC filter and resistive factor in the loop.

# Light Load Condition in Auto-Skip Operation (TPS51275/C)

The TPS51275/C automatically reduces switching frequency during light-load conditions to maintain high efficiency. This reduction of frequency is achieved smoothly and without an increase in output voltage ripple. A more detailed description of this operation is as follows. As the output current decreases from heavy-load condition, the inductor current is also reduced and eventually approaches valley zero current, which is the boundary between continuous conduction mode and discontinuous conduction mode. The rectifying MOSFET is turned off when this zero inductor current is detected. As the load current further decreases, the converter runs in discontinuous conduction mode and it takes longer and longer to discharge the output capacitor to the level that requires the next ON cycle. The ON time is maintained the same as that in the heavy-load condition. In reverse, when the output current increase from light load to heavy load, the switching frequency increases to the preset value as the inductor current reaches to the continuous conduction. The transition load point to the light load operation  $I_{OUT(LL)}$  (i.e. the threshold between continuous and discontinuous conduction mode) can be calculated as shown in Equation 1.

$$I_{OUT(LL)} = \frac{1}{2 \times L \times f_{SW}} \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}}$$

where

• f<sub>SW</sub> is the PWM switching frequency

(1)

Switching frequency versus output current during light-load conditions is a function of inductance (L), input voltage ( $V_{IN}$ ) and output voltage ( $V_{OUT}$ ), but it decreases almost proportional to the output current from the  $I_{OUT(LL)}$ .

#### ZHCS982B – JUNE 2012 – REVISED MARCH 2013

### Light-Load Condition in Out-of-Audio<sup>™</sup> Operation (TPS51275B)

Out-of-Audio<sup>TM</sup> (OOA) light-load mode is a unique control feature that keeps the switching frequency above acoustic audible frequencies toward a virtual no-load condition. During Out-of-Audio<sup>TM</sup> operation, the OOA control circuit monitors the states of both high-side and low-side MOSFETs and forces them switching if both MOSFETs are off for more than 40  $\mu$ s. When both high-side and low-side MOSFETs are off for 40  $\mu$ s during a light-load condition, the operation mode is changed to FCCM. This mode change initiates one cycle of the low-side MOSFET and the high-side MOSFET turning on. Then, both MOSFETs stay turned off waiting for another 40  $\mu$ s.

| Table 1. SKIP Mode Operation (TPS51275/B/C) |

|---------------------------------------------|

|---------------------------------------------|

|           | SKIP MODE OPERATION |

|-----------|---------------------|

| TPS51275  | Auto-skip           |

| TPS51275B | OOA                 |

| TPS51275C | Auto-skip           |

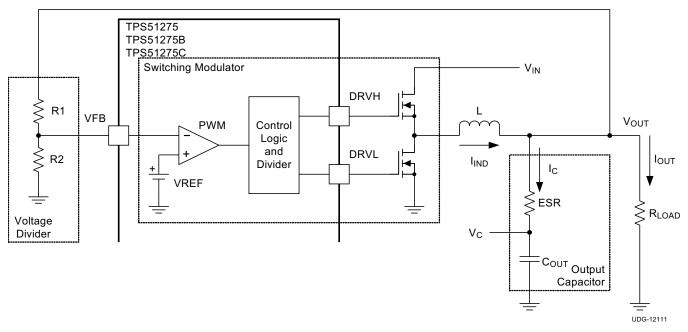

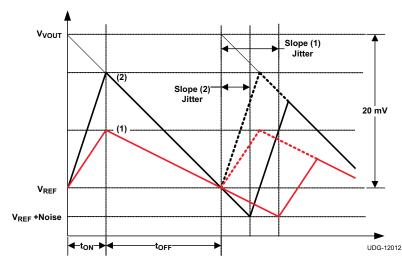

### D-CAP<sup>™</sup> Mode

From small-signal loop analysis, a buck converter using D-CAP<sup>™</sup> mode can be simplified as shown in Figure 1.

The output voltage is compared with internal reference voltage after divider resistors, R1 and R2. The PWM comparator determines the timing to turn on the high-side MOSFET. The gain and speed of the comparator is high enough to keep the voltage at the beginning of each ON cycle substantially constant. For the loop stability, the 0dB frequency,  $f_0$ , defined in Equation 2 must be lower than 1/4 of the switching frequency.

$$f_0 = \frac{1}{2\pi \times \text{ESR} \times C_{\text{OUT}}} \le \frac{f_{\text{SW}}}{4}$$

(2)

As  $f_0$  is determined solely by the output capacitor characteristics, the loop stability during D-CAP<sup>TM</sup> mode is determined by the capacitor chemistry. For example, specialty polymer capacitors have output capacitance in the order of several hundred micro-Farads and ESR in range of 10 milli-ohms. These yield an  $f_0$  value on the order of 100 kHz or less and the loop is stable. However, ceramic capacitors have  $f_0$  at more than 700 kHz, which is not suitable for this operational mode.

#### ZHCS982B-JUNE 2012-REVISED MARCH 2013

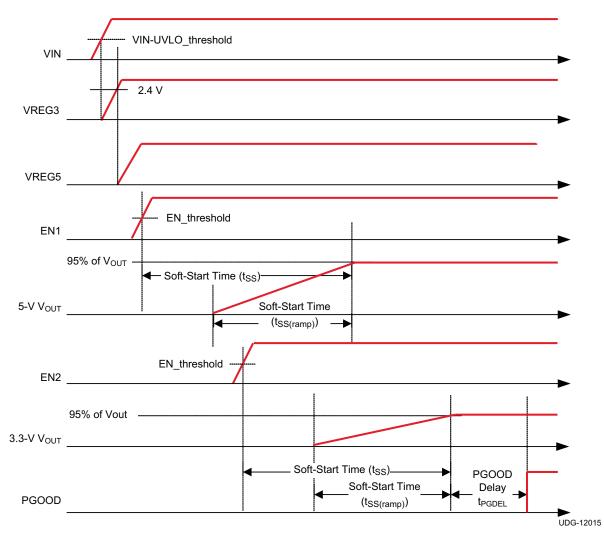

#### Enable and Powergood

VREG3 is an always-on regulator (TPS51275), VREG3/VREG5 are always-on regulators (TPS51275B/C), when the input voltage is beyond the UVLO threshold it turns ON. VREG5 is turned ON when either EN1 or EN2 enters the ON state (TPS51275). The VCLK signal initiates when EN1 enters the ON state (TPS51275/B/C). Enable states are shown in Table 2 through Table 3.

#### Table 2. Enabling/PGOOD State (TPS51275)

| EN1 | EN2 | VREG5 | VREG3 | CH1 (5Vout) | CH2 (3.3Vout) | VCLK | PGOOD |

|-----|-----|-------|-------|-------------|---------------|------|-------|

| OFF | OFF | OFF   | ON    | OFF         | OFF           | OFF  | Low   |

| ON  | OFF | ON    | ON    | ON          | OFF           | ON   | Low   |

| OFF | ON  | ON    | ON    | OFF         | ON            | OFF  | Low   |

| ON  | ON  | ON    | ON    | ON          | ON            | ON   | High  |

### Table 3. Enabling/PGOOD State (TPS51275B/C)

| EN1 | EN2 | VREG5 | VREG3 | CH1 (5Vout) | CH2 (3.3Vout) | VCLK | PGOOD |

|-----|-----|-------|-------|-------------|---------------|------|-------|

| OFF | OFF | ON    | ON    | OFF         | OFF           | OFF  | Low   |

| ON  | OFF | ON    | ON    | ON          | OFF           | ON   | Low   |

| OFF | ON  | ON    | ON    | OFF         | ON            | OFF  | Low   |

| ON  | ON  | ON    | ON    | ON          | ON            | ON   | High  |

# TPS51275, TPS51275B, TPS51275C

ZHCS982B - JUNE 2012 - REVISED MARCH 2013

Figure 3. TPS51275B/C Timing

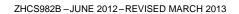

### Soft-Start and Discharge

The TPS51275/B/C operates an internal, 0.8-ms, voltage servo soft-start for each channel. When the ENx pin becomes higher than the enable threshold voltage, an internal DAC begins ramping up the reference voltage to the PWM comparator. Smooth control of the output voltage is maintained during start-up. When ENx becomes lower than the lower level of threshold voltage, TPS51275/B/C discharges outputs using internal MOSFETs through VO1 (CH1) and SW2 (CH2).

## VREG5/VREG3 Linear Regulators

There are two sets of 100-mA standby linear regulators which output 5 V and 3.3 V, respectively. The VREG5 pin provides the current for the gate drivers. The VREG3 pin functions as the main power supply for the analog circuitry of the device. VREG3 is an *Always ON* LDO and TPS51275B/C has *Always ON* VREG5. (See Table 2 and Table 3)

Add ceramic capacitors with a value of 1  $\mu$ F or larger (X5R grade or better) placed close to the VREG5 and VREG3 pins to stabilize LDOs.

The VREG5 pin switchover function is asserted when three conditions are present:

- CH1 internal PGOOD is high

- CH1 is not in OCL condition

- VO1 voltage is higher than VREG5-1V

In this switchover condition three things occur:

- the internal 5-V LDO regulator is shut off

- the VREG5 output is connected to VO1 by internal switchover MOSFET

- VREG3 input pass is changed from VIN to VO1

## VCLK for Charge Pump

The 260-kHz VCLK signal can be used in the charge pump circuit. The VCLK signal becomes available when EN1 is on state. The VCLK driver is driven by VO1 voltage. In a design that does not require VCLK output, leave the VCLK pin open.

## **Overcurrent Protection**

TPS51275/B/C has cycle-by-cycle over current limiting control. The inductor current is monitored during the OFF state and the controller maintains the OFF state during the inductor current is larger than the overcurrent trip level. In order to provide both good accuracy and cost effective solution, TPS51275/B/C supports temperature compensated MOSFET  $R_{DS(on)}$  sensing. The CSx pin should be connected to GND through the CS voltage setting resistor,  $R_{CS}$ . The CSx pin sources CS current ( $I_{CS}$ ) which is 10 µA typically at room temperature, and the CSx terminal voltage ( $V_{CS} = R_{CS} \times I_{CS}$ ) should be in the range of 0.2 V to 2 V over all operation temperatures. The trip level is set to the OCL trip voltage ( $V_{TRIP}$ ) as shown in Equation 3.

$$V_{\text{TRIP}} = \frac{R_{\text{CS}} \times I_{\text{CS}}}{8} + 1 \,\text{mV}$$

(3)

The inductor current is monitored by the voltage between GND pin and SWx pin so that SWx pin should be connected to the drain terminal of the low-side MOSFET properly. The CS pin current has a 4500 ppm/°C temperature slope to compensate the temperature dependency of the  $R_{DS(on)}$ . GND is used as the positive current sensing node so that GND should be connected to the source terminal of the low-side MOSFET.

As the comparison is done during the OFF state,  $V_{TRIP}$  sets the valley level of the inductor current. Thus, the load current at the overcurrent threshold,  $I_{OCP}$ , can be calculated as shown in Equation 4.

$$I_{OCP} = \frac{V_{TRIP}}{R_{DS(on)}} + \frac{I_{IND(ripple)}}{2} = \frac{V_{TRIP}}{R_{DS(on)}} + \frac{1}{2 \times L \times f_{SW}} \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}}$$

(4)

In an overcurrent condition, the current to the load exceeds the current to the output capacitor thus the output voltage tends to fall down. Eventually, it ends up with crossing the undervoltage protection threshold and shutdown both channels.

#### ZHCS982B - JUNE 2012 - REVISED MARCH 2013

#### **Output Overvoltage/Undervoltage Protection**

TPS51275/B/C asserts the overvoltage protection (OVP) when VFBx voltage reaches OVP trip threshold level. When an OVP event is detected, the controller changes the output target voltage to 0 V. This usually turns off DRVH and forces DRVL to be on. When the inductor current begins to flow through the low-side MOSFET and reaches the negative OCL, DRVL is turned off and DRVH is turned on. After the on-time expires, DRVH is turned off and DRVL is turned on again. This action minimizes the output node undershoot due to LC resonance. When the VFBx reaches 0V, the driver output is latched as DRVH off, DRVL on. The undervoltage protection (UVP) latch is set when the VFBx voltage remains lower than UVP trip threshold voltage for 250 µs or longer. In this fault condition, the controller latches DRVH low and DRVL low and discharges the outputs. UVP detection function is enabled after 1.35 ms of SMPS operation to ensure startup.

#### Undervoltage Lockout (UVLO) Protection

TPS51275/B/C has undervoltage lock out protection at VIN, VREG5 and VREG3. When each voltage is lower than their UVLO threshold voltage, both SMPS are shut-off. They are non-latch protections.

#### **Over-Temperature Protection**

TPS51275/B/C features an internal temperature monitor. If the temperature exceeds the threshold value (typically 155°C), TPS51275/B/C is shut off including LDOs. This is non-latch protection.

ZHCS982B-JUNE 2012-REVISED MARCH 2013

### **External Components Selection**

The external components selection is relatively simple for a design using D-CAP™ mode.

#### Step 1. Determine the Value of R1 and R2

The recommended R2 value is between 10 k $\Omega$  and 20 k $\Omega$ . Determine R1 using Equation 5.

$$R1 = \frac{(V_{OUT} - 0.5 \times V_{RIPPLE} - 2.0)}{2.0} \times R2$$

(5)

#### Step 2. Choose the Inductor

The inductance value should be determined to give the ripple current of approximately 1/3 of maximum output current and less than half of OCL (valley) threshold. Larger ripple current increases output ripple voltage, improves signal/noise ratio, and helps ensure stable operation.

$$L = \frac{1}{I_{IND(ripple)} \times f_{SW}} \times \frac{\left(V_{IN(max)} - V_{OUT}\right) \times V_{OUT}}{V_{IN(max)}} = \frac{3}{I_{OUT(max)} \times f_{SW}} \times \frac{\left(V_{IN(max)} - V_{OUT}\right) \times V_{OUT}}{V_{IN(max)}}$$

(6)

The inductor also needs to have low DCR to achieve good efficiency, as well as enough room above peak inductor current before saturation. The peak inductor current can be estimated as shown in Equation 7.

$$I_{\text{IND}(\text{peak})} = \frac{V_{\text{TRIP}}}{R_{\text{DS}(\text{on})}} + \frac{1}{L \times f_{\text{SW}}} \times \frac{\left(V_{\text{IN}(\text{max})} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN}(\text{max})}}$$

(7)

#### Step 3. Choose Output Capacitor(s)

Organic semiconductor capacitor(s) or specialty polymer capacitor(s) are recommended. Determine ESR to meet required ripple voltage. A quick approximation is as shown in Equation 8.

$$SR = \frac{V_{OUT} \times 20 \text{ mV} \times (1 - D)}{2 \text{ V} \times \text{I}_{\text{IND}(\text{ripple})}} = \frac{20 \text{ mV} \times \text{L} \times \text{f}_{SW}}{2 \text{ V}}$$

where

Е

• D as the duty-cycle factor

the required output ripple voltage slope is approximately 20 mV per t<sub>SW</sub> (switching period) in terms of VFB terminal

(8)

Figure 4. Ripple Voltage Slope and Jitter Performance

TEXAS INSTRUMENTS

www.ti.com.cn

ZHCS982B - JUNE 2012 - REVISED MARCH 2013

#### www.ti.com.cn

#### Layout Considerations

Good layout is essential for stable power supply operation. Follow these guidelines for an efficient PCB layout.

#### Placement

- Place voltage setting resistors close to the device pins.

- Place bypass capacitors for VREG5 and VREG3 close to the device pins.

#### Routing (Sensitive analog portion)

- Use small copper space for VFBx. There are short and narrow traces to avoid noise coupling.

- Connect VFB resistor trace to the positive node of the output capacitor. Routing inner layer away from power traces is recommended.

- Use short and wide trace from VFB resistor to vias to GND (internal GND plane).

#### **Routing (Power portion)**

- Use wider/shorter traces of DRVL for low-side gate drivers to reduce stray inductance.

- Use the parallel traces of SW and DRVH for high-side MOSFET gate drive in a same layer or on adjoin layers, and keep them away from DRVL.

- Use wider/ shorter traces between the source terminal of the high-side MOSFET and the drain terminal of the low-side MOSFET

- Thermal pad is the GND terminal of this device. Five or more vias with 0.33-mm (13-mils) diameter connected from the thermal pad to the internal GND plane should be used to have strong GND connection and help heat dissipation.

# TPS51275, TPS51275B, TPS51275C

ZHCS982B-JUNE 2012-REVISED MARCH 2013

XAS

Figure 10. Clock Frequency vs. Junction Temperature

# TPS51275, TPS51275B, TPS51275C

XAS

**STRUMENTS**

ZHCS982B-JUNE 2012-REVISED MARCH 2013

Figure 22. Switching Frequency vs. Output Current

Figure 21. Switching Frequency vs. Output Current

# TPS51275, TPS51275B, TPS51275C

www.ti.com.cn

EXAS

ZHCS982B-JUNE 2012-REVISED MARCH 2013

www.ti.com.cn

# APPLICATION DIAGRAM (TPS51275/TPS51275B/TPS51275C)

## Table 4. Key External Components (APPLICATION DIAGRAM (TPS51275/TPS51275B/TPS51275C))

| REFERENCE<br>DESIGNATOR | FUNCTION                                 | MANUFACTURER | PART NUMBER     |

|-------------------------|------------------------------------------|--------------|-----------------|

| L1                      | Output Inductor (5-V <sub>OUT</sub> )    | Alps         | GLMC3R303A      |

| L2                      | Output Inductor (3.3-V <sub>OUT</sub> )  | Alps         | GLMC2R203A      |

| C1                      | Output Capacitor (5-V <sub>OUT</sub> )   | SANYO        | 6TPE220MAZB x 2 |

| C2                      | Output Capacitor (3.3-V <sub>OUT</sub> ) | SANYO        | 6TPE220MAZB x 2 |

| Q1                      | MOSFET (5-V <sub>OUT</sub> )             | TI           | CSD87330Q3D     |

| Q2                      | MOSFET (3.3-V <sub>OUT</sub> )           | TI           | CSD87330Q3D     |

#### Copyright © 2012–2013, Texas Instruments Incorporated

ZHCS982B - JUNE 2012 - REVISED MARCH 2013

# **REVISION HISTORY**

| Cł | hanges from Original (JUNE 2011) to Revision A                                                    | Page |

|----|---------------------------------------------------------------------------------------------------|------|

| •  | Changed typographical error in V <sub>VREG3</sub> condition in ELECTRICAL CHARACTERISTICS table   | 5    |

| •  | Added V <sub>VREG3</sub> specification in ELECTRICAL CHARACTERISTICS table                        | 5    |

| •  | Changed updated inductor values in APPLICATION DIAGRAM (TPS51275/TPS51275B/TPS51275C) and Table 4 | 22   |

## Changes from Revision A (September 2012) to Revision B

| • | Changed 修订版本日期,从 2012 年 9 月改为 2013 年 3 月。 同时将 TPS51275B 添加至器件型号                          | 1  |

|---|------------------------------------------------------------------------------------------|----|

| • | Added (TPS151275/B/C) 至"特性"部分中的自动跳跃列表项                                                   | 1  |

| • | Added 全新的 OOA 列表项至"特性"部分                                                                 | 1  |

| • | Changed 整个文档内的 TPS51275/C 至 TPS51275/B/C                                                 | 1  |

| • | Changed 订购信息表。                                                                           | 1  |

| • | Changed the device number from TPS51275C TO TPS51275B/C in the elec chara table 2 places | 5  |

| • | Added TPS51275B to the PIN NO. column                                                    | 7  |

| • | Added OOA section after the Auto-Skip section                                            | 11 |

| • | Changed the APPLICATION DIAGRAM.                                                         | 22 |

|   |                                                                                          |    |

# **KAS** STRUMENTS

www.ti.com.cn

Page

# PACKAGING INFORMATION

| Orderable Device | Status | Package Type | •       | Pins | Package | Eco Plan     | Lead finish/  | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|--------------|---------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)          | Ball material | (3)                 |              | (4/5)          |         |

|                  |        |              |         |      |         |              | (6)           |                     |              |                |         |

| TPS51275BRUKR    | ACTIVE | WQFN         | RUK     | 20   | 3000    | RoHS & Green | NIPDAU        | Level-1-260C-UNLIM  | -40 to 125   | 1275B          | Samples |

| TPS51275BRUKT    | ACTIVE | WQFN         | RUK     | 20   | 250     | RoHS & Green | NIPDAU        | Level-1-260C-UNLIM  | -40 to 125   | 1275B          | Samples |

| TPS51275CRUKR    | ACTIVE | WQFN         | RUK     | 20   | 3000    | RoHS & Green | NIPDAU        | Level-1-260C-UNLIM  | -40 to 125   | 1275C          | Samples |

| TPS51275CRUKT    | ACTIVE | WQFN         | RUK     | 20   | 250     | RoHS & Green | NIPDAU        | Level-1-260C-UNLIM  | -40 to 125   | 1275C          | Samples |

| TPS51275RUKR     | ACTIVE | WQFN         | RUK     | 20   | 3000    | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 51275          | Samples |

| TPS51275RUKT     | ACTIVE | WQFN         | RUK     | 20   | 250     | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 51275          | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

www.ti.com

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

STRUMENTS

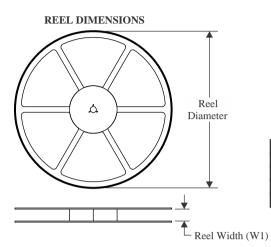

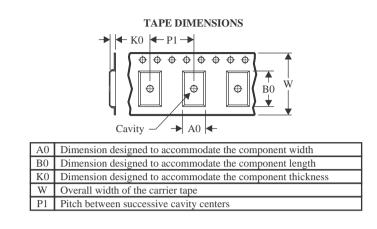

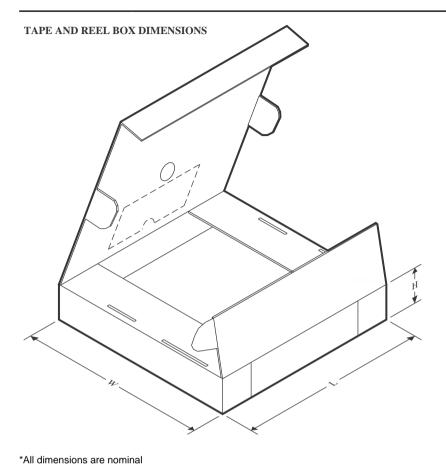

## TAPE AND REEL INFORMATION

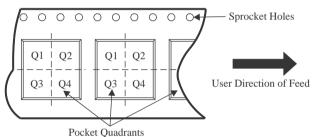

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS51275BRUKR               | WQFN            | RUK                | 20 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51275BRUKT               | WQFN            | RUK                | 20 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51275CRUKR               | WQFN            | RUK                | 20 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51275CRUKR               | WQFN            | RUK                | 20 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51275CRUKT               | WQFN            | RUK                | 20 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51275RUKR                | WQFN            | RUK                | 20 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51275RUKR                | WQFN            | RUK                | 20 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51275RUKT                | WQFN            | RUK                | 20 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51275RUKT                | WQFN            | RUK                | 20 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

www.ti.com

# PACKAGE MATERIALS INFORMATION

15-Sep-2023

| All dimensions are norminal |              |                 |      |      |             |            |             |

|-----------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| TPS51275BRUKR               | WQFN         | RUK             | 20   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS51275BRUKT               | WQFN         | RUK             | 20   | 250  | 210.0       | 185.0      | 35.0        |

| TPS51275CRUKR               | WQFN         | RUK             | 20   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS51275CRUKR               | WQFN         | RUK             | 20   | 3000 | 335.0       | 335.0      | 25.0        |

| TPS51275CRUKT               | WQFN         | RUK             | 20   | 250  | 210.0       | 185.0      | 35.0        |

| TPS51275RUKR                | WQFN         | RUK             | 20   | 3000 | 346.0       | 346.0      | 33.0        |

| TPS51275RUKR                | WQFN         | RUK             | 20   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS51275RUKT                | WQFN         | RUK             | 20   | 250  | 210.0       | 185.0      | 35.0        |

| TPS51275RUKT                | WQFN         | RUK             | 20   | 250  | 210.0       | 185.0      | 35.0        |

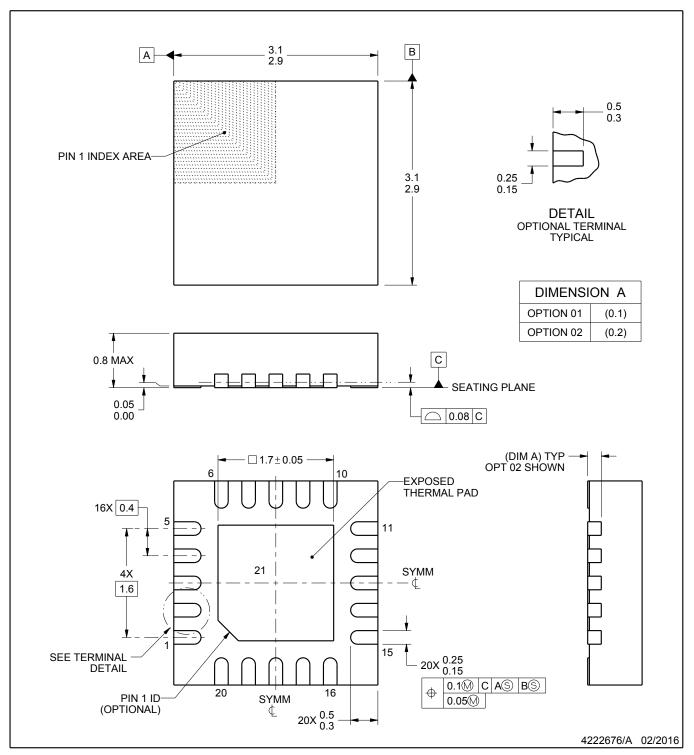

# **RUK0020B**

# **PACKAGE OUTLINE**

# WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

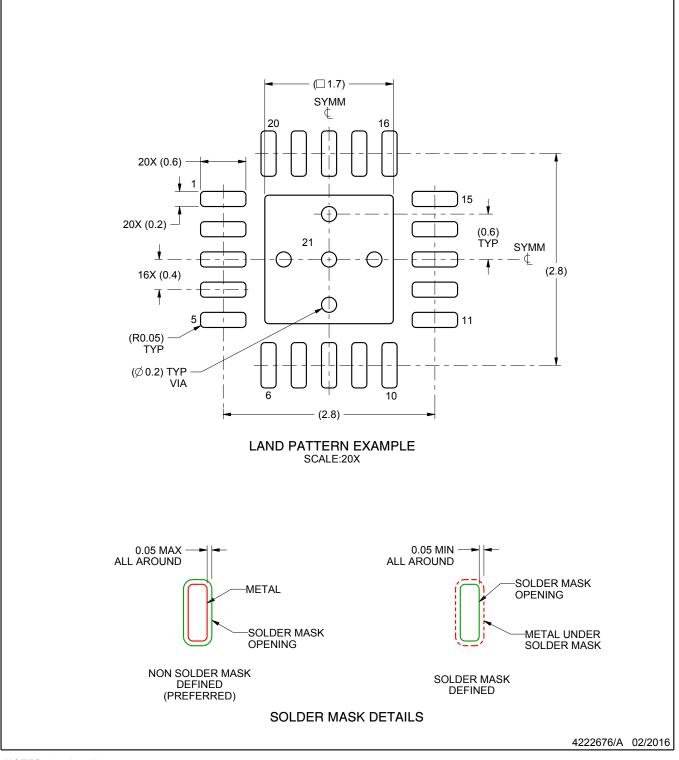

# **RUK0020B**

# **EXAMPLE BOARD LAYOUT**

# WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

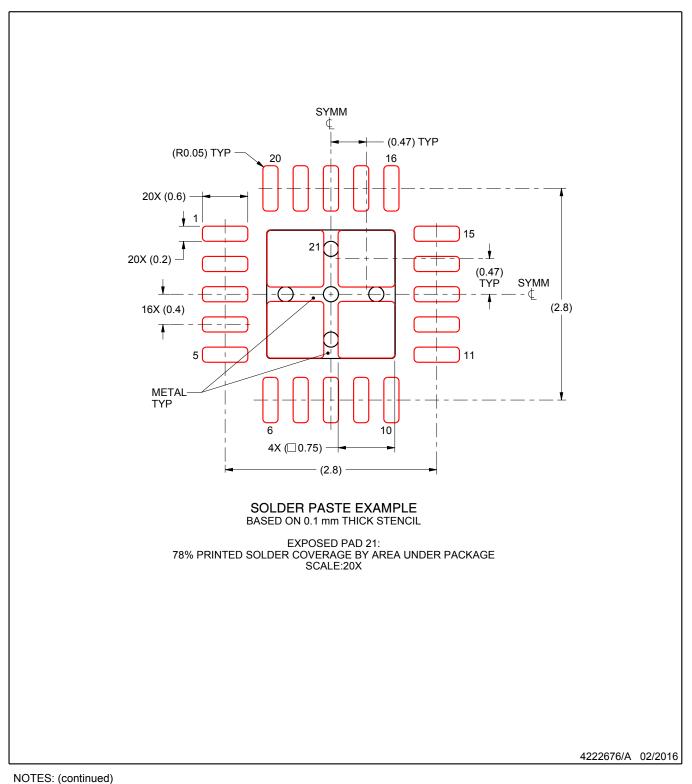

# **RUK0020B**

# **EXAMPLE STENCIL DESIGN**

# WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司