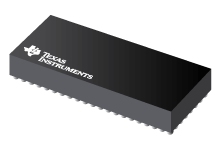

产品描述:

This 28-bit 1:2 configurable registered buffer is designed for 1.7-V to 1.9-V VCC operation. One device per DIMM is required to drive up to 18 stacked SDRAM loads or two devices per DIMM are required to drive up to 36 stacked SDRAM loads.

All inputs are SSTL_18, except the chip-select gate-enable (CSGEN), control (C), and reset (RESET) inputs, which are LVCMOS. All outputs are edge-controlled circuits optimized for unterminated DIMM loads, and meet SSTL_18 specifications, except the open-drain error (QERR) output.

The 74SSTUB32868A operates from a differential clock (CLK and CLK). Data are registered at the crossing of CLK going high and CLK going low.

The 74SSTUB32868A accepts a parity bit from the memory controller on the parity bit (PAR_IN) input, compares it with the data received on the DIMM-independent D-inputs (D1-D5, D7, D9-D12, D17-D28 when C = 0; or D1-D12, D17-D20, D22, D24-D28 when C = 1) and indicates whether a parity error has occurred on the open-drain QERR pin (active low). The convention is even parity; that is, valid parity is defined as an even number of ones across the DIMM-independent data inputs combined with the parity input bit. To calculate parity, all DIMM-independent D-inputs must be tied to a known logic state.

The 74SSTUB32868A includes a parity checking function. Parity, which arrives one cycle after the data input to which it applies, is checked on the PAR_IN input of the device. Two clock cycles after the data are registered, the corresponding QERR signal is generated.

If an error occurs and the QERR output is driven low, it stays latched low for a minimum of two clock cycles or until RESET is driven low. If two or more consecutive parity errors occur, the QERR output is driven low and latched low for a clock duration equal to the parity error duration or until RESET is driven low. If a parity error occurs on the clock cycle before the device enters the low-power mode (LPM) and the QERR output is driven low, it stays latched low for the LPM duration plus two clock cycles or until RESET is driven low. The DIMM-dependent signals (DCKE0, DCKE1, DODT0, DODT1, DCS0 and DCS1) are not included in the parity check computation.

The C input controls the pinout configuration from register-A configuration (when low) to register-B configuration (when high). The C input should not be switched during normal operation. It should be hard-wired to a valid low or high level to configure the register in the desired mode.

In the DDR2 RDIMM application, RESET is specified to be completely asynchronous with respect to CLK and CLK. Therefore, no timing relationship can be ensured between the two. When entering reset, the register is cleared and the data outputs is driven low quickly, relative to the time to disable the differential input receivers. However, when coming out of reset, the register becomes active quickly, relative to the time to enable the differential input receivers. As long as the data inputs are low, and the clock is stable during the time from the low-to-high transition of RESET until the input receivers are fully enabled, the design of the 74SSTUB32868A must ensure that the outputs remain low, thus ensuring no glitches on the output.

To ensure defined outputs from the register before a stable clock has been supplied, RESET must be held in the low state during power up.

The device supports low-power standby operation. When RESET is low, the differential input receivers are disabled, and undriven (floating) data, clock, and reference voltage (VREF) inputs are allowed. In addition, when RESET is low, all registers are reset and all outputs are forced low except QERR. The LVCMOS RESET and C inputs always must be held at a valid logic high or low level.

The device also supports low-power active operation by monitoring both system chip select (DCS0 and DCS1) and CSGEN inputs and will gate the Qn outputs from changing states when CSGEN, DCS0, and DCS1 inputs are high. If CSGEN, DCS0 or DCS1 input is low, the Qn outputs function normally. Also, if both DCS0 and DCS1 inputs are high, the device will gate the QERR output from changing states. If either DCS0 or DCS1 is low, the QERR output functions normally. The RESET input has priority over the DCS0 and DCS1 control and when driven low forces the Qn outputs low, and the QERR output high. If the chip-select control functionality is not desired, then the CSGEN input can be hard-wired to ground, in which case, the setup-time requirement for DCS0 and DCS1 would be the same as for the other D data inputs. To control the low-power mode with DCS0 and DCS1 only, then the CSGEN input should be pulled up to VCC through a pullup resistor.

The two VREF pins (A5 and AB5) are connected together internally by approximately 150  . However, it is necessary to connect only one of the two VREF pins to the external VREF power supply. An unused VREF pin should be terminated with a VREF coupling capacitor.

. However, it is necessary to connect only one of the two VREF pins to the external VREF power supply. An unused VREF pin should be terminated with a VREF coupling capacitor.

产品特性:

- 德州仪器Widebus+™系列成员

- Pinout优化DDR2 DIMM PCB布局

- 1对2输出支持堆叠DDR2 DIMM

- 芯片选择输入抑制状态变化的数据输出,限度降低系统功耗

- 输出边控电路限度降低非端接线路中的开关噪声

- 支持SSTL_18数据输入

- 差分时钟(CLK和CLK)输入

- 支持LVCMOS开关电平上的Chip-Select Gate-Enable, Control和RESET输入

- 检查内存无关数据输入的奇偶校验

- 支持工业温度范围(-40°C至85°C) RESET Input禁用差分输入接收,重置所有寄存器,并强制所有输出低,除了QERR

- APPLICATIONS

- 重载DDR2注册DIMM

Widebus+是Texas Instruments的商标。

所有其他商标均为其各自所有者的财产

功能内存接口

输出频率(Max)(频率)410

输出数量56

输出电源电压(V)1.8

核心供电电压(V)1.8

特性DDR2注册

温度范围(C)-40to85

等级产品样本

输出类型SSTL-18

输入类型SSTL-18

中文

中文 EN

EN

当前位置:

当前位置:

立即询价

立即询价 pdf下载

pdf下载 正在供货

正在供货 微信

微信 QQ

QQ 在线

在线

370791121

370791121 2119841551

2119841551