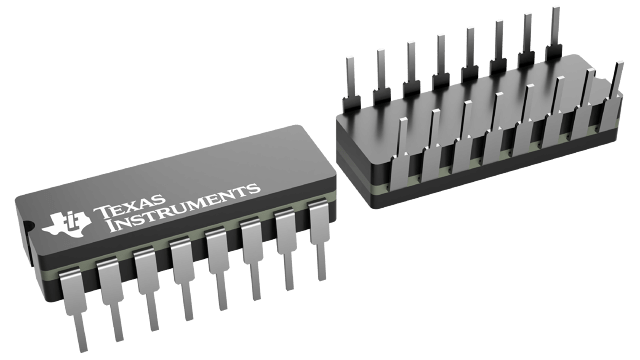

产品描述:

CD74ACT297为高精度、数字、锁相环应用提供了一种简单、经济实惠的解决方案。该器件包含构建一阶锁相环所需的所有电路(N分频计数器除外),如图1所示。

提供异或鉴相器(XORPD)和边沿控制(ECPD)鉴相器,以实现最大的灵活性。

环路功能的正确划分,以及封装外部的许多构建块,使设计者可以轻松地合并纹波消除或级联到更高阶锁相环。

递增/递减K计数器的长度可根据K计数器功能表进行数字编程。当A、B、C和D均为低电平时,K计数器被禁用。在A为高,B、C和D为低的情况下,K计数器只有三级长,这扩大了带宽或捕获范围,并缩短了环路的锁定时间。当A、B、C和D被编程为高电平时,K计数器变为17级长,这缩小了带宽或捕获范围,并延长了锁定时间。通过操作A-to-D输入实时控制环路带宽可以最大化数字锁相环的整体性能。 该器件无需使用模拟元件即可实现经典的一阶锁相环功能。数字锁相环(DPLL)的精度不受V和温度变化的影响,而仅取决于K时钟(K CLK)、递增/递减时钟(I/D CLK)和环路传播延迟的精度。I/D时钟频率和除以N的模数决定了DPLL的中心频率。中心频率由关系式fc=I/D时钟/2N(Hz)定义。产品特性:

- 双极FCT, AS和S的速度,显著降低功耗

- 数字设计避免模拟补偿误差

- 易于级联高阶环路

- 有用频率范围

- DC至110 MHz典型(K CLK)

- DC至70 MHz典型(I/D CLK)

- 动态可变带宽

- 可达到的非常窄的带宽

- 上电复位

- 输出能力

- 标准:XORPD OUT, ECPD OUT

- 总线驱动器:I/D OUT

- 可控硅抗锁存CMOS工艺与电路设计

- 平衡传播延迟

- ESD保护超过2000v / MIL-STD-883,方法3015

技术系列ACT

Bits(#)1

供电电压(Min)(V)4.5

供电电压(Max)(V)5.5

输入类型TTL-CompatibleCMOS

输出类型推挽式

供应电流(Max)(µA)80

有效输入电压(Max)(毫安)24

IOH(Max)(毫安)-24

中文

中文 EN

EN

当前位置:

当前位置:

立即询价

立即询价 pdf下载

pdf下载 正在供货

正在供货 微信

微信 QQ

QQ 在线

在线

370791121

370791121 2119841551

2119841551