产品描述:

SN65LVDS301串行化器件可将27个并行数据输入转换为1、2或3个子低电压差分信号(SubLVDS)串行输出。它从并行CMOS输入接口向移位寄存器加载24个像素位和3个控制位。除了27个数据位之外,该器件还将一个奇偶校验位和两个保留位添加到30位数据字中。每个字由像素时钟(PCLK)锁存到器件中。奇偶校验位(奇校验位)允许接收器检测单比特错误。根据使用的串行链路数,以像素时钟数据速率的30倍、15倍或10倍上传串行移位寄存器。像素时钟的副本在单独的差动输出上输出。

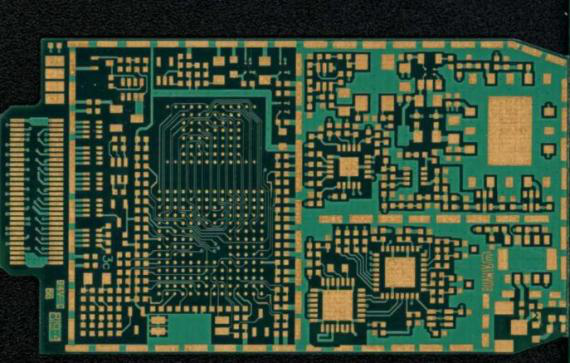

FPC布线通常将SN65LVDS301与显示器互连。与并行信号相比,LVDS301的输出显著降低了互连的EMI,降低幅度超过20分贝。该装置本身的电磁辐射很低,符合SAE J1752/3-M规范。(见图6-22)

SN65LVDS301的特点是可在-40°C至85°C的环境空气温度下工作。所有CMOS输入均提供故障保护功能,以保护它们在上电期间免受损坏,并避免在上电期间电流流入器件输入。当VDD介于0V和1.65V之间时,最高可将2.165 V的输入电压施加到所有cmos输入。

产品特性:

- FlatLink™3G串行接口技术

- 兼容FlatLink3G接收器,如SN65LVDS302

- 输入支持24位RGB视频模式接口

- 24位RGB数据,3个控制位,1个奇偶校验位和2个保留位通过1传输,2或3差分线

- subvds差分电压水平

- 有效数据吞吐量高达1755 Mbps

- 三种工作模式,以节省电力

- 三种工作模式,以节省电力

- 关闭模式0.5µA(类型)

- 待机模式0.5µA(类型)

- 总线交换增加PCB布局灵活性

- 1.8 v供电电压

- ESD额定值>2 kV (HBM)

- 像素时钟范围4mhz - 65mhz

- 所有CMOS输入Failsafe

- 封装:80引脚5mm × 5mm nFBGA

- 非常低的EMI符合SAE J1752/3 ' M ' -spec

功能Serializer

协议Channel-LinkI

供电电压(V)1.8

信号速率(MBits)1755

输入signalCMOS

输出signalLVDS

等级产品样本

温度范围(°C)-40to85

中文

中文 EN

EN

当前位置:

当前位置:

立即询价

立即询价 pdf下载

pdf下载 正在供货

正在供货 微信

微信 QQ

QQ 在线

在线

370791121

370791121 2119841551

2119841551