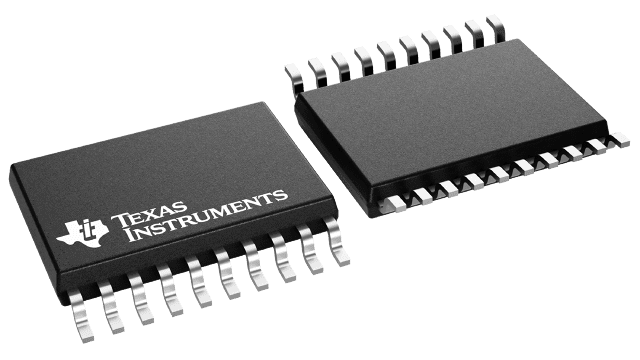

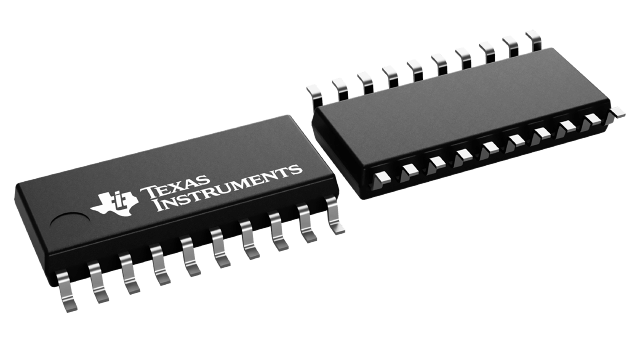

description of products:

The LV573A devices are octal transparent D-type latches designed for 2-V to 5.5-V VCC operation.

These devices feature 3-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads. They are particularly suitable for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers.

While the latch-enable (LE) input is high, the Q outputs follow the data (D) inputs. When LE is taken low, the Q outputs are latched at the logic levels set up at the D inputs.

A buffered output-enable (OE)\ input can be used to place the eight outputs in either a normal logic state (high or low logic levels) or high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly. The high-impedance state and the increased drive provide the capability to drive bus lines without need for interface or pullup components.

OE\ does not affect internal operations of the latch. Old data can be retained or new data can be entered while the outputs are in the high-impedance state.

To ensure the high-impedance state during power up or power down, OE\ should be tied to VCC through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

These devices are fully specified for partial-power-down applications using Ioff. The Ioff circuitry disables the outputs, preventing damaging current backflow through the devices when they are powered down.

product feature:

- 2-V to 5.5-V VCC Operation

- Max tpd of 8 ns at 5 V

- Typical VOLP (Output Ground Bounce)

<0.8 V at VCC = 3.3 V, TA = 25°C - Typical VOHV (Output VOH Undershoot)

>2.3 V at VCC = 3.3 V, TA = 25°C - Supports Mixed-Mode Voltage Operation on All Ports

- Ioff Supports Partial-Power-Down Mode Operation

- Latch-Up Performance Exceeds 250 mA Per JESD 17

- ESD Protection Exceeds JESD 22

- 2000-V Human-Body Model (A114-A)

- 200-V Machine Model (A115-A)

- 1000-V Charged-Device Model (C101)

通道数量8

技术系列LV-A

供电电压(Min)(V)2

供电电压(Max)(V)5.5

输入类型StandardCMOS

输出类型3-State

Clockfrequency(Max)(频率)70

有效输入电压(Max)(毫安)16

IOH(Max)(毫安)-16

供应电流(Max)(µA)20

特性Balancedoutputs,Highspeed(tpd10-50ns),Over-电压tolerantinputs,Partialpowerdown(Ioff),Flow-throughpinout

3003988121

3003988121