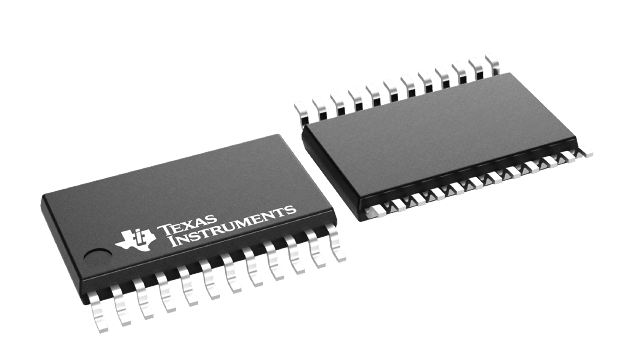

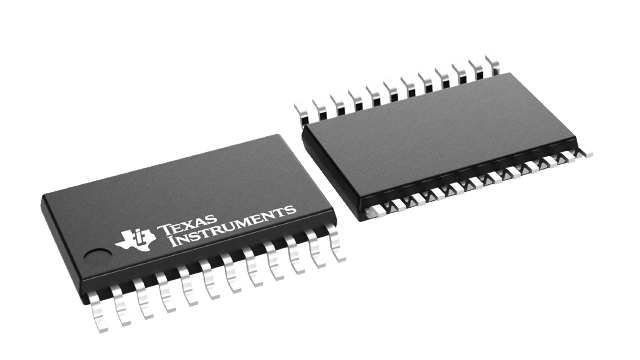

产品描述:

CDCVF855是一款高性能、低偏差、低抖动、零延迟的缓冲器,它将一对差分时钟输入对(CLK,CLK)分配给4对差分时钟输出对(Y[0:3],Y[0:3])和一对差分反馈时钟输出对(fbout,fbout)。时钟输出由时钟输入(CLK,CLK)、反馈时钟(FBIN,FBIN)和模拟电源输入(AVDD)控制。当PWRDWN为高电平时,输出将使用CLK进行同相和频率切换。当PWRDWN为低电平时,所有输出均禁用为高阻抗状态(3状态),并且PLL关闭(低功耗模式)。当输入频率低于建议的低于20 MHz(通常为10 MHz)的检测频率时,该器件也会进入此低功耗模式。输入频率检测电路检测低频状态,在施加20 MHz输入信号后,该检测电路打开PLL并启用输出。

当AVDD为低电平时,出于测试目的,PLL关闭并绕过。CDCVF855还能够跟踪扩展频谱时钟,以降低EMI。

由于CDCVF855基于锁相环电路,所以需要一段稳定时间才能实现锁相环的锁相。通电后需要此稳定时间。CDCVF855的特点是可用于商业和工业温度范围。

产品特性:

- Spread-Spectrum Clock Compatible

- Operating Frequency: 60 MHz to 220 MHz

- Low Jitter (Cycle-Cycle): ±60 ps (±40 ps at 200 MHz)

- Low Static Phase Offset: ±50 ps

- Low Jitter (Period): ±60 ps (±30 ps at 200 MHz)

- 1-to-4 Differential Clock Distribution (SSTL2)

- Best in Class for VOX = VDD/2 ±0.1 V

- Operates From Dual 2.6-V or 2.5-V Supplies

- Available in a 28-Pin TSSOP Package

- Consumes < 100-µA Quiescent Current

- External Feedback Pins (FBIN, FBIN) Are Used to Synchronize the Outputs to the Input Clocks

- Meets/Exceeds JEDEC Standard (JESD82-1) For DDRI-200/266/333 Specification

- Meets/Exceeds Proposed DDRI-400 Specification (JESD82-1A)

- Enters Low-Power Mode When No CLK Input Signal Is Applied or PWRDWN Is Low

- APPLICATIONS

- DDR Memory Modules (DDR400/333/266/200)

- Zero-Delay Fan-Out Buffer

功能零延迟

AdditiveRMS抖动(规格)(fs)65

输出频率(Max)(频率)220

输出数量4

输出电源电压(V)1.7

核心供电电压(V)2.5

输出偏斜(ps)40

特性Spreadspectrumclocking(SSC)

温度范围(C)-40to85

等级产品样本

输出类型LVTTL

输入类型LVTTL

中文

中文 EN

EN

当前位置:

当前位置:

立即询价

立即询价 pdf下载

pdf下载 正在供货

正在供货 微信

微信 QQ

QQ 在线

在线

370791121

370791121 2119841551

2119841551