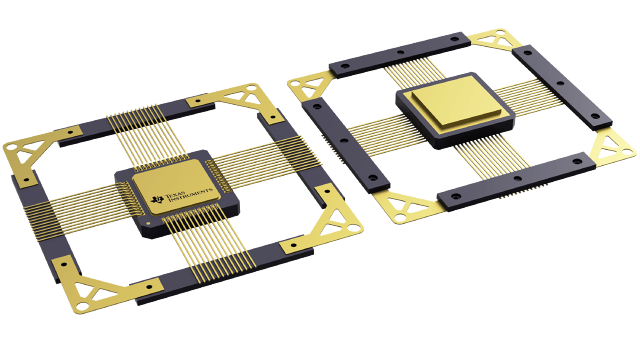

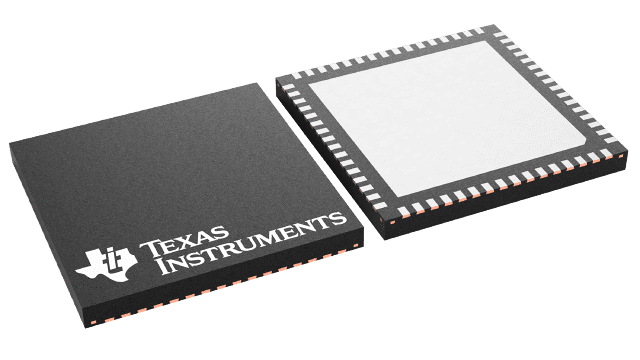

产品描述:

LMK04832-SEP 是一款适用于航天应用、支持 JEDEC JESD204B/C 的高性能时钟调节器。

PLL2 可以配置 14 个时钟输出以驱动 7 个 JESD204B/C 转换器或其他逻辑器件(使用器件和 SYSREF 时钟)。SYSREF 可以通过直流和交流耦合提供。14 个输出中的每一个输出都可以单独配置为用于传统时钟系统的高性能输出(不限于 JESD204B/C 应用)。

无论有无 SYSREF 生成或重新计时,该器件都可以配置为在双 PLL、单 PLL 或时钟分配模式下运行。PLL2 可以使用内部或外部 VCO 工作。

高性能与多种特性(如功耗和性能权衡调节、双 VCO、动态数字延迟和保持)相结合,可提供灵活的高性能时钟树。

产品特性:

- VID#:V62/22612

- 电离辐射总剂量 30krad(无 ELDRS)

- SEL 抗扰度 > 43MeV × cm2/mg

- SEFI 抗扰度 > 43MeV × cm2/mg

- 环境温度范围:-55°C 至 125°C

- 时钟输出频率:3255MHz

- 多模式:双 PLL、单 PLL 和时钟分配

- 6GHz 外部 VCO 或分配输入

- 超低噪声(2500MHz 时):

- 54fs RMS 抖动(12kHz 至 20MHz)

- 64fs RMS 抖动(100Hz 至 20MHz)

- –157.6dBc/Hz 本底噪声

- 超低噪声(3200MHz 时):

- 61fs RMS 抖动(12kHz 至 20MHz)

- 67fs RMS 抖动(100Hz 至 100MHz)

- –156.5dBc/Hz 本底噪声

- PLL2

- –230dBc/Hz PLL FOM

- –128dBc/Hz PLL 1/f

- 相位检测器频率高达 320MHz

- 两个集成 VCO:2440MHz 至 2600MHz 和 2945MHz 至 3255MHz

- 多达 14 个差分器件时钟

- CML、LVPECL、LCPECL、HSDS、LVDS 和 2xLVCMOS 可编程输出

- 最多 1 个缓冲 VCXO/XO 输出

- LVPECL、LVDS、2xLVCMOS 可编程输出

- 1-1023 CLKOUT 分频器

- 1-8191 SYSREF 分频器

- SYSREF 时钟 25ps 阶跃模拟延迟

- 器件时钟和 SYSREF 数字延迟和动态数字延迟

- PLL1 保持模式

- PLL1 或 PLL2 0 延迟

- 高可靠性

- 受控基线

- 一个组装/测试场所

- 一个制造场所

- 延长的产品生命周期

- 延长的产品变更通知

- 产品可追溯性

功能Dual-loopPLL,Ultra-lowjitterclockgenerator

输出数量15

RMS抖动(fs)54

输出频率(Max)(频率)3255

输入类型HCSL,LVCMOS,LVCMOS(REF_CLK),LVDS,LVPECL,LVPECL(VCXO_CLK)

输出类型CML,HSDS,LVCMOS,LVDS,LVPECL

供电电压(Min)(V)3.135

供电电压(Max)(V)3.465

特性0Delay,集成振荡器,JESD204B,Lossofsignaldetection,Manual/autoswitch,控可编程Delay,SPI

温度范围(C)-55to125,25to25

中文

中文 EN

EN

当前位置:

当前位置:

立即询价

立即询价 pdf下载

pdf下载 正在供货

正在供货 微信

微信 QQ

QQ 在线

在线

370791121

370791121 2119841551

2119841551