产品描述:

TL16C554和TL16C554I是TL16C550B异步通信元件(ACE)的增强版。每个通道对从外围设备或调制解调器接收的数据字符执行串并转换,并对CPU传输的数据字符执行并串转换。在功能运行期间,CPU可以随时读取四路ACE的每个通道的完整状态。获取的信息包括执行的操作的类型和条件以及遇到的任何错误条件。

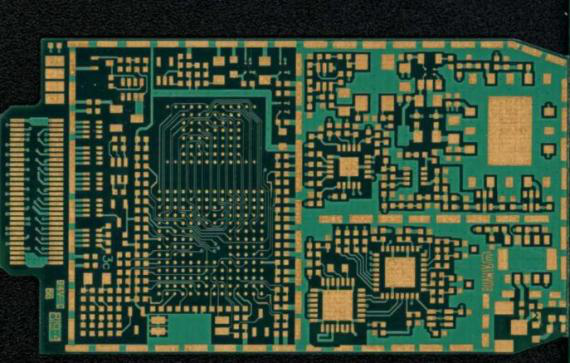

TL16C554和TL16C554I四重ACE可置于备用FIFO模式,从而激活内部FIFO以允许在接收和发送模式下存储16字节(加上接收器FIFO中每个字节的3位错误数据)。为了最大限度地减少系统开销和最大限度地提高系统效率,所有逻辑都在芯片上。两个终端功能允许发送直接存储器访问(DMA)传输的信号。每个ACE包括一个可编程波特率发生器,可将定时参考时钟输入除以1和(216-1)之间的除数。TL16C554和TL16C554I采用68针塑料引线芯片载体(PLCC)FN封装和80针(TQFP)PN封装。

产品特性:

- Integrated Asynchronous Communications Element

- Consists of Four Improved TL16C550 ACEs Plus Steering Logic

- In FIFO Mode, Each ACE Transmitter and Receiver Is Buffered With 16-Byte FIFO to Reduce the Number of Interrupts to CPU

- In TL16C450 Mode, Hold and Shift Registers Eliminate Need for Precise Synchronization Between the CPU and Serial Data

- Up to 16-MHz Clock Rate for up to 1-Mbaud Operation

- Programmable Baud Rate Generators Which Allow Division of Any Input Reference Clock by 1 to (216-1) and Generate an Internal 16 × Clock

- Adds or Deletes Standard Asynchronous Communication Bits (Start, Stop, and Parity) to or From the Serial Data Stream

- Independently Controlled Transmit, Receive, Line Status, and Data Set Interrupts

- Fully Programmable Serial Interface Characteristics:

- 5-, 6-, 7-, or 8-Bit Characters

- Even-, Odd-, or No-Parity Bit

- 1-, 1 1/2-, or 2-Stop Bit Generation

- Baud Generation (DC to 1-Mbit Per Second)

- False Start Bit Detection

- Complete Status Reporting Capabilities

- Line Break Generation and Detection

- Internal Diagnostic Capabilities:

- Loopback Controls for Communications Link Fault Isolation

- Break, Parity, Overrun, Framing Error Simulation

- Fully Prioritized Interrupt System Controls

- Modem Control Functions (CTS\, RTS\, DSR\, DTR\, RI\, and DCD\)

- 3-State Outputs Provide TTL Drive Capabilities for Bidirectional Data Bus and Control Bus

通道数量4

FIFO(Byte)16

RxFIFOtriggerlevels(#)4

控可编程FIFOtriggerlevelsNo

CPUinterfaceX86

BaudrateatVcc=5V&with16xsampling(max)(MBits)1

Operating电压(V)5

AutoRTS/CTSNo

等级产品样本

温度范围(°C)-40to85,0to70

中文

中文 EN

EN

当前位置:

当前位置:

立即询价

立即询价 pdf下载

pdf下载 正在供货

正在供货 微信

微信 QQ

QQ 在线

在线

370791121

370791121 2119841551

2119841551