产品描述:

TLV320AIC3101是一款低功耗立体声音频编解码器,配有立体声耳机功放,AS 以及可编程为单端或全差分的多个输入和输出 配置。包括广泛的基于寄存器的功率控制,支持立体声48 kHz DAC 3.3V模拟电源的播放功率低至14 mW,是便携式电池供电的理想选择 音频和电话应用程序。

TLV320AIC3101的记录路径包含数字集成麦克风偏置 带MIX/MUX的受控立体声麦克风前置放大器和自动增益控制(AGC) 在多个模拟输入之间的能力。可编程滤镜在录制期间可用, 可以消除数码相机光学变焦过程中可能出现的声音噪音。回放 PATH包括来自立体声DAC和选定输入的混合/多路复用器功能,通过可编程 音量控制,到各种输出。 TLV320AIC3101包含四个大功率输出驱动器以及两个完整的 差分输出驱动器。高功率输出驱动器能够驱动各种负载 配置,包括最多四通道使用交流耦合的单端16-Ω耳机 电容器,或无盖输出配置的立体声16-Ω耳机。此外,成对的 驱动器可用于驱动btl配置中的8-Ω扬声器,每通道功率为500 mW。 立体声音频DAC支持从8 kHz到96 kHz的采样率,并包括 DAC路径中的可编程数字滤波,可实现3D、低音、高音、中音效果、扬声器 32-kHz、44.1-khz和48-khz采样率的均衡和去加重。立体声音频ADC 支持8 khz到96 khz的采样率,前面有可编程增益放大器或AGC 这可以为低电平麦克风输入提供高达59.5分贝的模拟增益。TLV320AIC3101 为攻击(8秒1,408毫秒)和衰落提供极高范围的可编程性 (0.05-22.4秒)。此扩展AGC范围允许针对多种类型的AGC进行调整 应用程序。用于模拟或数字信号处理都不需要的省电应用 需要时,可将该设备置于特殊的模拟信号通过模式。此模式 极大地降低了功耗,因为在此期间大部分设备都会断电 直通操作。

串行控制总线支持I2C协议,而 串行音频数据总线可编程用于I2S,左/右对齐, DSP或TDM模式。包括高度可编程的PLL,以实现灵活的时钟生成和支持 对于来自各种可用MCLK的所有标准音频速率,从512 kHz到50 MHz不等, 特别关注最流行的12-MHz、13-MHz、16-MHz、19.2-MHz和 19.68-MHz系统时钟。

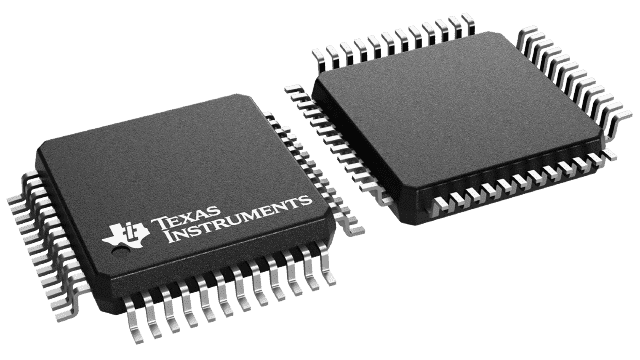

TLV320AIC3101采用2.7 V至3.6 V的模拟电源,数字核心电源为 1.525 V和1.95 V,数字I/O电源为1.1V和3.6V。该器件的尺寸为5 mm×5 mm 32针QFN封装。产品特性:

- Stereo Audio DAC

- 102-dBA Signal-to-Noise Ratio

- 16/20/24/32-Bit Data

- Supports Sample Rates From 8 kHz to 96 kHz

- 3D/Bass/Treble/EQ/De-Emphasis Effects

- Flexible Power Saving Modes and Performance

are Available

- Stereo Audio ADC

- 92-dBA Signal-to-Noise Ratio

- Supports Sample Rates From 8 kHz to 96 kHz

- Digital Signal Processing and Noise Filtering

Available During Record

- Six Audio Input Pins

- One Stereo Pair of Single-Ended Inputs

- One Stereo Pair of Fully Differential Inputs

- Six Audio Output Drivers

- Stereo Fully Differential or Single-Ended

Headphone Drivers - Fully Differential Stereo Line Outputs

- Stereo 8-Ω, 500-mW/Channel Speaker Drive

Capability

- Stereo Fully Differential or Single-Ended

- Low Power: 14-mW Stereo 48-kHz Playback With

3.3-V Analog Supply - Ultralow-Power Mode With Passive Analog Bypass

- Programmable Input/Output Analog Gains

- Automatic Gain Control (AGC) for Record

- Programmable Microphone Bias Level

- Programmable PLL for Flexible Clock Generation

- I2C Control Bus

- Audio Serial Data Bus Supports I2S,

Left/Right-Justified, DSP, and TDM Modes - Extensive Modular Power Control

- Power Supplies:

- Analog: 2.7 V–3.6 V.

- Digital Core: 1.525 V–1.95 V

- Digital I/O: 1.1 V–3.6 V

- Package: 5-mm × 5-mm 32-Pin QFN

ADC通道数量2

数字模拟转换器(DAC)通道数量2

DigitalaudiointerfaceL,R,I2S,DSP,TDM

模拟inputs6

Samplingrate(Max)(kHz)96

等级产品样本

特性Notchfilter,Matrixmixing,Phase-lockedloop(PLL),Stereospeakeramplifier,Stereoheadphoneamplifier

ADCSNR(规格)(dB)92

DACSNR(规格)(dB)102

中文

中文 EN

EN

当前位置:

当前位置:

立即询价

立即询价 pdf下载

pdf下载 正在供货

正在供货 微信

微信 QQ

QQ 在线

在线

370791121

370791121 2119841551

2119841551